Рады представить Вашему вниманию программное обеспечение для разработки и отладки Libero SoC v11.4 SP1. В новой версии стал доступен корпус FCS536 для старших кристаллов SmartFusion2/IGLOO2. Другие существенные усовершенствования включают в себя методологию разделения FPGA-дизайна для имплементации и верификации, усовершенствования ПО такие, как автономная инициализация MDDR, FDDR и SERDESIF, и новые возможности программирования для SmartFusion2 и IGLOO2. Также, в Release Notes описаны известные проблемы с блоками SERDES и подсистемами MSS/HPMS и представлены варианты их решения. Наряду со средой разработки были обновлены FlashPro v11.4 и Firmware Catalog v11.4. Более подробная информация об изменениях и ссылка для скачивания новой версии Libero SoC доступны в Release Notes: http://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc#downloads

Настройка временных констрейнов в Libero SoC

для СнК SmartFusion2 и ПЛИС IGLOO2

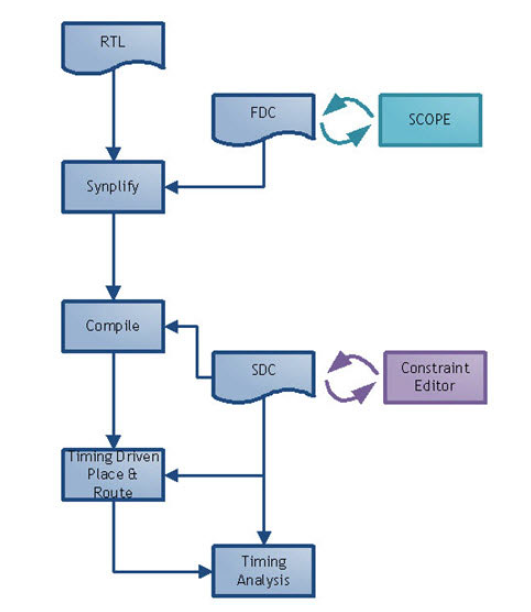

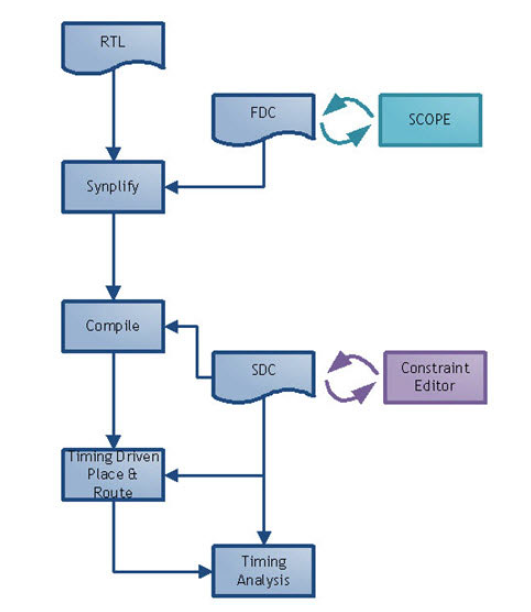

При создании синхронных цифровых устройств на базе ПЛИС, от наброска дизайна до физической реализации, довольно редко удаётся сразу достичь требуемой производительности. Для этого обычно необходимо провести несколько итераций всего цикла разработки — проектирование, логический синтез, трассировка и временной анализ. Задание временных констрейнов (Timing Constraints) и проведение временного анализа (Timing Analysis) — два наиболее важных этапа разработки синхронного FPGA-дизайна. Если после очередной итерации требования к производительности не выполняются, необходимо обдумать усовершенствование и добавление новых констрейнов и ещё раз повторить цикл. Задание некорректных временных констрейнов может привести к неработоспособности или непредсказуемой работе устройства.

Инженеры Microsemi рекомендуют задавать временные констрейны как для этапа синтеза, так и для этапа трассировки. В помощь разработчику на базе ПЛИС Microsemi выпущено новое руководство пользователя по заданию временных констрейнов в Libero SoC для СнК SmartFusion2 и ПЛИС IGLOO2. Руководство доступно по ссылке:

http://www.microsemi.com/document-portal/doc_download/134356-smartfusion2-igloo2-fpga-timing-constraints-user-s-guide Выпуск Libero 11.4 SP1 и новое руководство пользователя Рады представить Вашему вниманию программное обеспечение для разработки и отладки Libero SoC v11.4 SP1. В новой версии стал доступен корпус FCS536 для старших кристаллов SmartFusion2/IGLOO2. Другие существенные усовершенствования включают в себя методологию разделения FPGA-дизайна для имплементации и верификации, усовершенствования ПО такие, как автономная инициализация MDDR, FDDR и SERDESIF, и новые возможности программирования для SmartFusion2 и IGLOO2. Также, в Release Notes описаны известные проблемы с блоками SERDES и подсистемами MSS/HPMS и представлены варианты их решения. Наряду со средой разработки были обновлены FlashPro v11.4 и Firmware Catalog v11.4. Более подробная информация об изменениях и ссылка для скачивания новой версии Libero SoC доступны в Release Notes: http://www.microsemi.com/products/fpga-soc/design-resources/design-software/libero-soc#downloads Настройка временных констрейнов в Libero SoC для СнК SmartFusion2 и ПЛИС IGLOO2 При создании синхронных цифровых устройств на базе ПЛИС, от наброска дизайна до физической реализации, довольно редко удаётся сразу достичь требуемой производительности. Для этого обычно необходимо провести несколько итераций всего цикла разработки — проектирование, логический синтез, трассировка и временной анализ. Задание временных констрейнов (Timing Constraints) и проведение временного анализа (Timing Analysis) — два наиболее важных этапа разработки синхронного FPGA-дизайна. Если после очередной итерации требования к производительности не выполняются, необходимо обдумать усовершенствование и добавление новых констрейнов и ещё раз повторить цикл. Задание некорректных временных констрейнов может привести к неработоспособности или непредсказуемой работе устройства. Инженеры Microsemi рекомендуют задавать временные констрейны как для этапа синтеза, так и для этапа трассировки. В помощь разработчику на базе ПЛИС Microsemi выпущено новое руководство пользователя по заданию временных констрейнов в Libero SoC для СнК SmartFusion2 и ПЛИС IGLOO2. Руководство доступно по ссылке: http://www.microsemi.com/document-portal/doc_download/134356-smartfusion2-igloo2-fpga-timing-constraints-user-s-guide