### Intel<sup>®</sup> 82571EB/82572EI Ethernet Controller

**Specification Update**

December 2008 Revision 6.0

### Legal Information

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINCEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different Hyper-Threading Technology requires a computer system with an Intel<sup>®</sup> Pentium<sup>®</sup> 4 processor supporting HT Technology and a HT Technology enabled chipset, BIOS and operating system. Performance will vary depending on the specific hardware and software you use. See http://www.intel.com/products/ ht/Hyperthreading\_more.htm for additional information.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order. Copies of documents that have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation

P.O. Box 5937 Denver, CO 80217-9808

Or by visiting Intel's website at http://www.intel.com; or by calling: North America 1-800-548-4725, Europe 44-0-1793-431-155, France 44-0-1793-421-777, Germany 44-0-1793-421-333, other Countries 708-296-9333.

Intel and Intel logo are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries. \*Other names and brands may be claimed as the property of others.

Copyright  $\ensuremath{\textcircled{C}}$  2004-2008, Intel Corporation. All Rights Reserved.

### **Revision History**

| Revision | Revision Date | Description                                                                                                                                                                                                                                                                                                                                                                                             |  |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.0      | Jan 2004      | Initial release.                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1.1      | Jan 2004      | Added Erratum 16; Sightings 4-6.                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1.2      | Feb 2004      | Added Erratum 17-18; Added Device Identification and Mechanicals                                                                                                                                                                                                                                                                                                                                        |  |

| 1.3      | Mar 2004      | Added B-1 errata.                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1.4      | Apr 2004      | Added erratum 23 and 24. Added stepping information on summary of changes table.                                                                                                                                                                                                                                                                                                                        |  |

| 1.5      | May 2004      | Removed references to 82570EI.<br>Updated Erratum #14.                                                                                                                                                                                                                                                                                                                                                  |  |

| 1.6      | Jun 2004      | Added erratum #30. Moved sightings #1, 2, 3, 6, 7, and 8 to erratum # 21, 25, 26, 27, 28, and 29, respectively. Removed sighing # 4.                                                                                                                                                                                                                                                                    |  |

| 1.7      | Jul 2004      | Fixed the summary of table changes. Appended updated schematics.                                                                                                                                                                                                                                                                                                                                        |  |

| 1.8      | Jan 2005      | Removed errata that were fixed for C0. Added new errata found on C0. Added 82572EI information.                                                                                                                                                                                                                                                                                                         |  |

| 1.9      | Jun 2005      | Removed errata fixed for C0. Added new errata for D0.                                                                                                                                                                                                                                                                                                                                                   |  |

| 2.0      | Sep 2005      | Added errata 48 through 75, sightings 15 through 18 and specification clarifications 4, 5 & 6.                                                                                                                                                                                                                                                                                                          |  |

| 2.1      | Feb 2006      | Removed all pre-production completed/fixed items and renumbered the remaining items; added Specification Change 1; added Errata 35, 36 & 37; moved information about Specification Clarification 6—"On-Die Cable Discharge Event protection may not be sufficient" to design guide; changed Sighting 17 to Errata 37; removed Sighting 18: it was caused by a test setup issue; clarified some wording. |  |

| 2.2      | Jun 2006      | Added Specification Change #2 (iSCSI Header Split Not Supported) and Change #3 (EEPROM Initialization). Added Errata 38-44. Added Specification Clarifications #6 & #7.                                                                                                                                                                                                                                 |  |

| 2.3      | Nov 2006      | Added Errata 45-56 and Specification Clarification 8.                                                                                                                                                                                                                                                                                                                                                   |  |

| 3.0      | March 2007    | Added Errata 57-64 and Specification Clarification 9; corrected device names in MM number table; added alternative workaround for errata #7; added definition for "image" in table 2.                                                                                                                                                                                                                   |  |

| 4.0      | October 2007  | Added Errata 65-67.                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 5.0      | January 2008  | Added Errata 68 and Specification Clarifications 10 & 11.                                                                                                                                                                                                                                                                                                                                               |  |

| 6.0      | December 2008 | Added Specification Change 4. Added Errata 69, 70, 71, 72 and 73; added Specification Clarifications 12 and 13: updated Errata 7, 18, and 66.                                                                                                                                                                                                                                                           |  |

### 1. Preface

This document applies to both the Intel<sup>®</sup> 82571EB and 82572EI Gigabit Ethernet controllers. They are commonly referred to as the device. Any information that applies to only one will be noted as such.

This document is an update to published specifications. Specification documents for this product include:

- 82571EB/82572EI Gigabit Ethernet Controller Product Preview Datasheet, Intel Corporation.

- 82571EB/82572EI Gigabit Ethernet Controller Design Guide, Intel Corporation.

- PCIe\* Family of Gigabit Ethernet Controllers Software Developer's Manual, Intel Corporation

This document is intended for hardware system manufacturers and software developers of applications, operating systems or tools. It may contain Specification Changes, Errata, and Specification Clarifications.

All product documents are subject to frequent revision, and new order numbers will apply. New documents may be added. Be sure you have the latest information before finalizing your design.

### 2. Nomenclature

This document uses various definitions, codes, and abbreviations to describe the Specification Changes, Errata, Sightings and/or Specification Clarifications that apply to the listed silicon/steppings:

#### Table 2-1. Definitions

| Name                                                                                                                                                                                                                                                              | Description                                                                                                                          |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| Specification<br>Changes                                                                                                                                                                                                                                          | Modifications to the current published specifications. These changes will be incorporated in the next release of the specifications. |  |

| Errata Design defects or errors. Errata may cause device behavior to deviate from publishe specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices. |                                                                                                                                      |  |

| Specification<br>Clarifications Greater detail or further highlights concerning a specification's impact to a comp<br>design situation. These clarifications will be incorporated in the next release of<br>specifications.                                       |                                                                                                                                      |  |

| Documentation<br>ChangesTypos, errors, or omissions from the current published specifications. These chan<br>be incorporated in the next release of the specifications.                                                                                           |                                                                                                                                      |  |

### 3. Codes and Abbreviations

| Name                        | Description                                                                                         |  |

|-----------------------------|-----------------------------------------------------------------------------------------------------|--|

| Х                           | Specification Change, Erratum, or Specification Clarification that applies to this stepping.        |  |

| Doc                         | Document change or update that will be implemented.                                                 |  |

| Fix                         | This erratum is intended to be fixed in a future stepping of the component.                         |  |

| Fixed                       | This erratum has been previously fixed.                                                             |  |

| NoFix                       | There are no plans to fix this erratum.                                                             |  |

| Image                       | Erratum in the EEPROM image or one the can be fixed with an updated EEPROM image.                   |  |

| Eval                        | Plans to fix this erratum are under evaluation.                                                     |  |

| (No mark) or<br>(Blank box) | This erratum is fixed in listed stepping or specification change does not apply to listed stepping. |  |

| Shaded                      | This Item is either new or modified from the previous version of the document.                      |  |

| DS                          | Data Sheet                                                                                          |  |

| DG                          | Design Guide                                                                                        |  |

| SDM                         | Software Developer's Manual                                                                         |  |

| EDS                         | External Data Specification                                                                         |  |

| AP                          | Application Note                                                                                    |  |

### 4. Device Identification

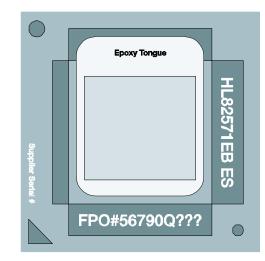

The following tables and drawings describe the various identifying markings on each device package:

#### Table 4-1. Markings

| Device                                                                                                                                                                                                                                                                                                           | Stepping          | Top Marking | <b>Q-Specification</b> | Notes               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|------------------------|---------------------|

| 82571EB                                                                                                                                                                                                                                                                                                          | D0<br>(lead free) | JL82571EB   | Q866                   | Engineering Samples |

| 82571EB                                                                                                                                                                                                                                                                                                          | D0                | HL82571EB   | Q864                   | Engineering Samples |

| 82572EI                                                                                                                                                                                                                                                                                                          | D0<br>(lead free) | JL82572EI   | Q867                   | Engineering Samples |

| 82572EI                                                                                                                                                                                                                                                                                                          | D0                | HL82572EI   | Q865                   | Engineering Samples |

| 82571EB                                                                                                                                                                                                                                                                                                          | D0<br>(lead free) | JL82571EB   | N/A                    | Production          |

| 82571EB                                                                                                                                                                                                                                                                                                          | D0                | HL82571EB   | N/A                    | Production          |

| 82572EI                                                                                                                                                                                                                                                                                                          | D0<br>(lead free) | JL82572EI   | N/A                    | Production          |

| 82572EI                                                                                                                                                                                                                                                                                                          | D0                | HL82572EI   | N/A                    | Production          |

| <b>Note:</b> The devices can also have a "82571GB" or "82572GI" marking (instead of "82571EB" or "82572EI"); the 82571GB and 82572GI devices are used only on Intel network interface adapters. The 82571GB is functionally equivalent to the 82571EB and the 82572GI is functionally equivalent to the 82572EI. |                   |             |                        |                     |

#### Table 4-2. Revision ID

| Device                                                   | Vendor<br>ID | Device ID | Revision ID* |  |  |

|----------------------------------------------------------|--------------|-----------|--------------|--|--|

| 82571EB D0 (copper applications)                         | 8086         | 105E      | 6            |  |  |

| 82571EB D0 (fiber applications)                          | 8086         | 105F      | 6            |  |  |

| 82571EB D0 (SERDES backplane applications)               | 8086         | 1060      | 6            |  |  |

| 82572EI D0 (copper applications)                         | 8086         | 107D      | 6            |  |  |

| 82572EI D0 (fiber applications)                          | 8086         | 107E      | 6            |  |  |

| 82572EI D0 (SERDES backplane applications)               | 8086         | 107F      | 6            |  |  |

| *= Revision ID is located at Config address 0x8 bits 7:0 |              |           |              |  |  |

#### Table 4-3. MM Numbers

| Product   | Tray MM# | Tape and Reel MM# |

|-----------|----------|-------------------|

| HL82571EB | 875300   | 875296            |

| HL82572EI | 875302   | 875297            |

| JL82571EB | 875303   | 875298            |

| JL82572EI | 875304   | 875299            |

#### Figure 4-1. Example 82571EB/82572EI Identifying Marks

- **Note:** Lead-free parts will have "JL" as the prefix for the product code (vs. "HL") and the "Q" designator refers to the Q Specification number in the table above.

- **Note:** The devices can also have a "82571GB" or "82572GI" marking (instead of "82571EB" or "82572EI"); the 82571GB and 82572GI devices are used only on Intel network interface adapters. The 82571GB is functionally equivalent to the 82571EB and the 82572GI is functionally equivalent to the 82572EI.

### 5. Summary Table of Changes

| No. | D0 | Plans | Specification Changes                                                                                                                                                 | Page |

|-----|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1   | Х  | Doc   | SMBus Operation at 1MHz Not Supported.                                                                                                                                | 13   |

| 2   | Х  | Doc   | iSCSI Header Split Is Not Supported                                                                                                                                   | 13   |

| 3   | х  | Doc   | The EEPROM Initialization Control 2 (word 0Fh) bit 7 is<br>Reserved and Must Be Set To 0.                                                                             | 15   |

| 4   | Х  | Doc   | 82571EB ECC Protection Enable 0x1100                                                                                                                                  |      |

| No. | DO | Plans | Errata                                                                                                                                                                | Page |

| 1   | Х  | NoFix | When Two Functions Have Differing MAX_PAYLOAD_SIZE, the Device Might Use the Larger Value For All Functions.                                                          | 17   |

| 2   | х  | NoFix | Upstream Attempt to Reconfigure the PCIe Link by Moving the Link Training Status State Machine (LTSSM) from Recovery To Configuration Will Cause a "Link Down" Event. | 17   |

| 3   | Х  | NoFix | When Using Serial Over LAN, the Device's Power State Can Be Ambiguous.                                                                                                | 17   |

| 4   | х  | NoFix | PCIe Differential- and Common-Mode Return Loss Is Higher than Specified Value.                                                                                        | 18   |

| 5   | Х  | NoFix | SerDes Transmit Differential Return Loss Is Higher than Specified Value.                                                                                              | 18   |

| 6   | Х  | NoFix | SerDes Is Unable To Acquire Sync From Ordered Sets Beginning With /K28.1/.                                                                                            | 18   |

| 7   | х  | NoFix | Device Transmit Operation Might Halt in TCP Segmentation<br>Offload (TSO) Mode when Multiple Requests Are Enabled.                                                    | 19   |

| 8   | Х  | NoFix | IDE-Redirect Persistent Retransmission Inconsistency.                                                                                                                 | 19   |

| 9   | Х  | NoFix | SMBus Transactions Might Be NACKed (Not ACKnowledged)<br>Under IDE and SMBus Stress.                                                                                  | 19   |

| 10  | х  | NoFix | I2C Transactions: When Working with Bus Speed 400KHz or<br>Higher, Bus Might Hang when the Master Reads More Bytes<br>than the Slave Reported.                        | 20   |

| 11  | Х  | NoFix | SOL Timeout Character Control Byte In EEPROM Image Does Not Function.                                                                                                 | 20   |

| 12  | Х  | NoFix | Incorrect Number of Retransmissions of Link-Down Alert.                                                                                                               | 20   |

| 13  | Х  | NoFix | Device Does Not Support PCIe Active State Power Management<br>L1 State (ASPM L1).                                                                                     | 21   |

| 14  | Х  | NoFix | XOFF from Partner Can Prevent Flow-Control (XON/XOFF)<br>Transmission.                                                                                                | 21   |

| 15  | Х  | NoFix | Missed RX Packets.                                                                                                                                                    | 22   |

| 16 | х | NoFix | Tx Stops during Host Management Stress in 10Mbps Half-<br>Duplex.                                                                    | 22 |

|----|---|-------|--------------------------------------------------------------------------------------------------------------------------------------|----|

| 17 | х | NoFix | Device Overwrites Port A LAA to Default Value Due to Port B Software Reset.                                                          | 23 |

| 18 | х | NoFix | Enabling or Disabling RSS in the Middle of Received Packets<br>May Stop Receive Flow.                                                | 26 |

| 19 | Х | NoFix | Packets with IPV6-Tunneled-in-IPV4 with a Certain Value Of<br>Last IP Options Will Have an Incorrect RSS Hash Value.                 | 26 |

| 20 | Х | NoFix | Formed and Invalid /C/ Code Handling on the SerDes Interface.                                                                        | 26 |

| 21 | Х | NoFix | False Detection of idle_match Condition on the SerDes Interface.                                                                     | 27 |

| 22 | Х | NoFix | Ability Match and Acknowledge Match on the SerDes Interface.                                                                         | 27 |

| 23 | Х | NoFix | Frames with Alignment Errors.                                                                                                        | 28 |

| 24 | х | NoFix | Inter-Frame Spacing (10/100 Half-Duplex Mode).                                                                                       | 28 |

| 25 | Х | NoFix | Auto Cross Sample Timer (PHY-related issue).                                                                                         | 28 |

| 26 | Х | NoFix | Firmware Reset Occurs when Performing Transactions with a Low Interpacket Gap (IPG) Using Fast Management Link (FML) at 8MHz.        | 28 |

| 27 | Х | NoFix | 10-base TLink Pulse Hits the Template Mask Due to Voltage Ripple/Glitch.                                                             | 29 |

| 28 | Х | NoFix | 10base-T TP_IDL Template Failure.                                                                                                    | 30 |

| 29 | Х | NoFix | BMC Fragments that Are Sent Through Two Different SMBus<br>Ports Are Sent Over LAN as a Single Packet.                               | 30 |

| 30 | Х | NoFix | Frames with Variations in the Preamble Are Rejected.                                                                                 | 30 |

| 31 | Х | NoFix | Reception of Undersized Frames Affects Good Frame Reception.                                                                         | 31 |

| 32 | Х | NoFix | Packet Length-Related Issues.                                                                                                        | 31 |

| 33 | Х | NoFix | When MANC.EN_XSUM_FILTER Is Not Enabled, Received<br>Packets With Wrong UDP Checksum Are Transferred To BMC.                         | 31 |

| 34 | Х | NoFix | Device Sends Only One XOFF Even if the Link Partner Has<br>Timed Out and It Is Still Congested.                                      | 32 |

| 35 | х | NoFix | When Wake on LAN (WoL) Is Disabled, the Device Consumes<br>More Than the Specified 20mA.                                             | 32 |

| 36 | Х | NoFix | The Device Does Not Correctly Handle Received Nullified<br>Transaction Layer Packets (TLP).                                          | 32 |

| 37 | х | NoFix | Link Down During Receive Flow May Cause Data Corruption.                                                                             | 33 |

| 38 | Х | Fixed | Incorrect PCIe Configurations Can Be Set by Earlier Versions of dev_starter EEPROM Images (v5.8 and below).                          | 33 |

| 39 | Х | NoFix | Packets Received with an L2+L3 Header Length Greater than 256 Bytes Can Incorrectly Report a Checksum Error.                         | 33 |

| 40 | х | NoFix | PCIe Bus Can Halt upon D3/L1 Entry If There Are Less Than 16<br>Posted Data (PD) Flow Control Credits (=256byte memory<br>writes).   | 34 |

| 41 | Х | Fixed | When APM Enable (WOL) is not set may affect the PCIe Configurations (dev_starter images v5.9 and below).                             | 34 |

| 42 | Х | Fixed | Traffic on SMBus While Link Is Down Causes Firmware Reset.                                                                           | 35 |

| 43 | Х | NoFix | SOL Stress Data Integrity Fails with IDER Stress.                                                                                    | 35 |

| 44 | х | NoFix | The 82571EB/82572EI PCIe Transmit Differential Voltage<br>Amplitude Is 1.4V (Maximum of 1.5V) for the First 15ms of<br>Transmission. | 35 |

| No. | DO | Plans   | Errata                                                                                                                                          | Page |

|-----|----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 45  | Х  | Image   | ARC Halts when SMBus Sslave Address is Set to 0x00.                                                                                             | 35   |

| 46  | х  | Image   | Rx Packet NotificationTimeout Does Not Reset after Master Reads Fragment.                                                                       | 36   |

| 47  | х  | Image   | BMC Configuration Commands are Discarded when there is<br>Heavy Manageability Traffic Load.                                                     | 36   |

| 48  | х  | Image   | Duplicate Fragments Might Be Sent to the BMC.                                                                                                   | 36   |

| 49  | Х  | Image   | Memory Buffer Leaks Under Heavy SMBus Traffic Load.                                                                                             | 36   |

| 50  | Х  | Image   | First Two Bytes of a Rx Packet Forwarded to the BMC Might Be Dropped, Degrading Performance.                                                    | 37   |

| 51  | х  | No Fix. | SMBus Might Hang if the BMC Is Reset in the Middle of a Transaction.                                                                            | 37   |

| 52  | х  | No Fix. | Certain Malformed IPV6 Extension Headers are not Processed<br>Correctly by the Device.                                                          | 37   |

| 53  | Х  | No Fix  | Completion with CA or UR Status Is Considered Malformed.                                                                                        | 38   |

| 54  | Х  | Image   | HMAC Calculation For RMCP+ Session Establishment Is Incorrect.                                                                                  | 38   |

| 55  | Х  | Image   | SOL Payload Fails to Activate with Encryption Activation Bit Set When Session Was Not Established with Encryption.                              | 38   |

| 56  | Х  | Image   | User Password Not Being Used (Instead of the Kg) when Calculating the SIK.                                                                      | 38   |

| 57  | Х  | Image   | Firmware Resets While Link Is Down                                                                                                              | 39   |

| 58  | Х  | Image   | Integrity Value in RMCP+ session establishment                                                                                                  | 39   |

| 59  | Х  | Image   | Username in RAKP1 Message Must Be Padded to 16 Bytes                                                                                            | 39   |

| 60  | Х  | Image   | Device Accepts Invalid User Name when RMCP+ Session Owner                                                                                       | 40   |

| 61  | Х  | Image   | Configuring RMCP+ Password from the BMC                                                                                                         | 40   |

| 62  | Х  | Image   | "Update User Password" Command Incorrectly Accepts Less<br>Than 20 Bytes of Data                                                                | 40   |

| 63  | Х  | No Fix  | Byte Enables 2 and 3 Are Not Set on MSI Writes                                                                                                  | 40   |

| 64  | Х  | No fix  | Wakeup Event Occurs on Magic Packet that Doesn't Pass<br>Address Filter                                                                         | 41   |

| 65  | Х  | No Fix  | SKP (SKIP ordered set) Will Reset TS (Training Sequence)<br>Count.                                                                              | 41   |

| 66  | Х  | No Fix  | 82571EB-82572EI Does Not Correctly Implement Master/Slave Resolution.                                                                           | 41   |

| 67  | Х  | No Fix  | 82571EB-82572EI Improperly Implements the Auto-<br>Negotiation Advertisement Register.                                                          | 42   |

| 68  | х  | No Fix  | PCIe: Occasionally, When Receiving a Corrupted Completion<br>with a TAG x to Another TAG "a" Might Result in Device Hang or<br>Data Corruption. | 42   |

| 69  | Х  | No Fix  | RDTR: No Write Back on RX Packet When Too Close to Previous Packets.                                                                            | 43   |

| 70  | Х  | No Fix  | 82571/82572 Overwrites Transmit Descriptors in Internal Buffer.                                                                                 | 43   |

| 71  | Х  | No Fix  | Link Indication: LED Remains On In D3 Power State in SerDes Mode.                                                                               | 44   |

| 72  | Х  | Х       | PCIe: Missing Replay Due to Recovery During TLP Transmission                                                                                    | 44   |

|     | Х  | х       | PCIe: LTSSM Moves from L0 to Recovery Only When Receiving                                                                                       | 44   |

|     |    |       |                                                                                                                                         | 1  |

|-----|----|-------|-----------------------------------------------------------------------------------------------------------------------------------------|----|

| No. | DO | Plans | Specification Clarifications                                                                                                            |    |

| 1   | Х  | Doc   | Disable Auto MDI-X for Forced 100BASE-TX Operation.Disable<br>Auto MDI-X for Forced 100BASE-TX Operation.                               | 45 |

| No. | D0 | Plans | Specification Clarifications                                                                                                            |    |

| 2   | Х  | Doc   | Request Will Not Be Treated As Completion Abort (CA) When the Programming Model Bytes Enable Is Violated.                               | 45 |

| 3   | Х  | Doc   | System-Level EMI Test Can Be Affected by 490MHz Harmonic Seen In 10Base-T Waveform Spectrum.                                            | 45 |

| 4   | Х  | Doc   | MDI Return Loss Is Marginal Near 40MHz at 1150hm Load.                                                                                  | 46 |

| 5   | Х  | Doc   | PCIe Output Driver Amplitude Can Be Set Incorrectly By the EEPROM.                                                                      | 46 |

| 6   | Х  | Doc   | Only One Port Can Be Disabled at a Time; LAN Disable<br>(LAN0_DIS_N & LAN1_DIS_N)—82571 Only                                            | 47 |

| 7   | х  | Doc   | Manageability Modes Not Available When System Is in S5 State when "device power down" Is Activated and APM Is Disabled.                 | 47 |

| 8   | Х  | Doc   | Manageability Not Supported on SMBus 1.                                                                                                 | 47 |

| 9   | Х  | Doc   | Support for WOL Concurrently on Both Ports                                                                                              | 47 |

| 10  | Х  | Doc   | LED Modes Based On LINK Speed Only Work in Copper(Internal PHY) Mode                                                                    | 48 |

| 11  | Х  | Doc   | THERM_Dp (D4) and THEMR_Dn (D5) are reserved and should not be used                                                                     | 48 |

| 12  | Х  | Doc   | TCP Segmentation Offload Operations With Both Transmit Queues Enabled.                                                                  | 48 |

| 13  | х  | Doc   | When Port 0 and Port 1 Are Connected Back-to-Back, the PHY Should Be Reset As Part of the Driver Initialization To Avoid Link Failures. | 49 |

### 6. Specification Changes

# 1. SMBus Operation at 1 Mhz Is Not Supported (400 kHz Operation Not Affected)

Operation of the SMBus at 1 MHz is not supported. Operation at the standard SMBus frequency (400 kHz) is not affected and is supported. The operation frequency is set by the EEPROM.

### 2. iSCSI Header Split Feature Is Not Supported

The extended Rx and Rx write-back descriptors are affected. This information supercedes the information in the *PCIe Family of Gigabit Ethernet Controllers Software Developer's Manual*, Section 3.2.6.5.

The following tables reflect the changes:

#### PKTTYPE (bit 19:16):

The PKTTYPE field defines the type of the packet that was detected by the device. It tries to find the most complex match until it locates the most common one, as shown in the Packet Type table below:

| Packet Type | Description                                       |

|-------------|---------------------------------------------------|

| 0x0         | MAC , (VLAN/SNAP) Payload                         |

| 0x1         | MAC, (VLAN/SNAP) Ipv4 , Payload                   |

| 0x2         | MAC, (VLAN/SNAP) Ipv4, TCP/UDP, payload           |

| 0x3         | MAC (VLAN/SNAP) ,Ipv4, Ipv6, payload              |

| 0x4         | MAC (VLAN/SNAP) ,Ipv4, Ipv6 ,TCP/UDP, payload     |

| 0x5         | MAC (VLAN/SNAP) , Ipv6, payload                   |

| 0x6         | MAC (VLAN/SNAP) , Ipv6 ,TCP/UDP, payload          |

| 0x8         | MAC, (VLAN/SNAP) Ipv4, TCP/UDP, NFS, payload      |

| 0xA         | MAC (VLAN/SNAP) ,Ipv4, Ipv6 ,TCP/UDP,NFS, payload |

| 0xC         | MAC (VLAN/SNAP), Ipv6, TCP/UDP, NFS, payload      |

*Note:* Payload does not mean raw data, but can be also an unsupported header.

Note: If there is NFS header in the packets, it can be seen in the packet type field.

**Packet types supported by the packet split**: The 82571/82572 provides header split for the packet types listed below. Other packet types are posted sequentially in the buffers of the packet split receive buffers.

| Packet<br>Type | Description                                       | Header Split                                                                                                                                   |

|----------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0            | MAC , (VLAN/SNAP) Payload                         | No                                                                                                                                             |

| 0x1            | MAC, (VLAN/SNAP) Ipv4 , Payload                   | Split header after L3 if fragmented packets                                                                                                    |

| 0x2            | MAC, (VLAN/SNAP) Ipv4, TCP/UDP, payload           | Split header after L4 if not fragmented,<br>otherwise treat as packet type 1                                                                   |

| 0x3            | MAC (VLAN/SNAP) ,Ipv4, Ipv6, payload              | Split header after L3 if either Ipv4 or Ipv6<br>indicates a fragmented packet                                                                  |

| 0x4            | MAC (VLAN/SNAP) ,Ipv4, Ipv6 ,TCP/UDP, payload     | Split header after L4 if Ipv4 not fragmented<br>and if Ipv6 does not include fragment<br>extension header, otherwise treat as packet<br>type 3 |

| 0x5            | MAC (VLAN/SNAP) , Ipv6, payload                   | Split header after L3 if fragmented packets                                                                                                    |

| 0x6            | MAC (VLAN/SNAP) , Ipv6 ,TCP/UDP, payload          | Split header after L4 if Ipv6 does not include<br>fragment extension header, otherwise treat<br>as packet type 5                               |

| 0x8            | MAC, (VLAN/SNAP) Ipv4, TCP/UDP, NFS, payload      | Split header after L5 if not fragmented,<br>otherwise treat as packet type 1                                                                   |

| 0xA            | MAC (VLAN/SNAP) ,Ipv4, Ipv6 ,TCP/UDP,NFS, payload | Split header after L5 if Ipv4 not fragmented<br>and if Ipv6 does not include fragment<br>extension header, otherwise treat as packet<br>type 3 |

| 0xC            | MAC (VLAN/SNAP) , Ipv6 ,TCP/UDP, NFS, payload     | Split header after L5 if Ipv6 does not include<br>fragment extension header, otherwise treat<br>as packet type 5                               |

As a result of this specification change, bits 5:0 of the Receive Filter Control Register are now reserved.

| Field       | Bit(s) | Initial Value                                                          | Description                                                                                                                                                                                                                                            |

|-------------|--------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserved    | 5:0    | 0                                                                      | <b>Reserved</b> . Should be written with 0 to ensure future compatibility.                                                                                                                                                                             |

| NFSW_DIS    | 6      | 0 NFS Write disable<br>Disable filtering of NFS write request headers. |                                                                                                                                                                                                                                                        |

| NFSR_DIS    | 7      | 0 NFS Read disable<br>Disable filtering of NFS read reply headers.     |                                                                                                                                                                                                                                                        |

| NFS_VER     | 9:8    | 00                                                                     | NFS Version<br>00 NFS version 2<br>01 NFS version 3<br>10 NFS version 4<br>11 Reserved for future use                                                                                                                                                  |

| IPv6_dis    | 10     | 0                                                                      | IPv6 disable.<br>Disable IPv6 packet filtering                                                                                                                                                                                                         |

| IP6Xsum_dis | 11     | 0                                                                      | IPv6 Xsum disable<br>Disable XSUM on IPv6 packets                                                                                                                                                                                                      |

| ACKDIS      | 12     | 0                                                                      | ACK accelerate disable<br>When this bit is set OPHIR will not accelerate interrupt on TCP ACK<br>packets.                                                                                                                                              |

| ACKD_DIS    | 13     | 0                                                                      | ACK data Disable<br>1 – OPHIR will recognize ACK packets according to the ACK bit in the<br>TCP header + No -CP data<br>0 - OPHIR will recognize ACK packets according to the ACK bit only.<br>This bit is relevant only if the ACKDIS bit is not set. |

| Field            | Bit(s) | Initial Value | Description                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------|--------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IPFRSP_DIS       | 14     | 0             | IP Fragment Split Disable<br>When this bit is set the header of IP fragmented packets will not be<br>set.                                                                                                                                                                                                                                                                                                         |

| EXSTEN           | 15     | 0             | Extended status Enable,<br>When the EXSTEN bit is set or when the Packet Split receive<br>descriptor is used, OPHIR writes the extended status to the Rx<br>descriptor.                                                                                                                                                                                                                                           |

| IPv6_ExdIS       | 16     | 0             | <ul> <li>IPv6 Extension Header Disable, Chicken bit to disable the IPv6 extension headers parsing for XSUM offload, Header split and Filtering:</li> <li>0 - parse and recognize allowed IPV6 extension headers (Hop-by-Hop, Destination Options, and Routing )</li> <li>1 - do not recognize above extension headers</li> </ul>                                                                                  |

| NEW_IPV6_EXT_DIs | 17     | 0             | <ul> <li>New IPv6 Extension Header, Chicken bit to disable the mobility<br/>IPv6 extension headers parsing, required for RSS:</li> <li>- parse and recognize IPV6 "home address option" and "rout2"<br/>extension headers for RSS function</li> <li>I f an IPv6 packet includes either a Home-Address-Option or a<br/>Routing-Header-Type-2, then the TcpIPv6Ex and IPv6Ex functions are<br/>not used.</li> </ul> |

### 3. The EEPROM Initialization Control 2 (word 0Fh) bit 7 is Reserved and Must Be Set To 0.

The EEPROM Initialization Control 2 (word 0Fh) bit 7 is reserved and must be set to 0.

Documents affected by this change are the PCIe Family of Ethernet Gigabit Controllers Software Developers Manual and the 82571EB/82572EI EEPROM Information Guide.

### 4. 82571EB ECC Protection Enable 0x1100

The Packet Buffer has ECC protection and uses a register at address 0x1100 to control the operation of the ECC:

| Field                   | Bit(s) | Initial Value                              | Description                                                                                                                                                                                                    |

|-------------------------|--------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ECC Error Counter       | 31:20  | 0x000                                      | Incremented on each ECC error detection, cleared by writing to bit 1 of this register.                                                                                                                         |

| Reserved                | 19     | 1                                          | Reserved write to 1                                                                                                                                                                                            |

| ECC Disable From EEPROM | 18     | Loaded from EEPROM word<br>0x10/0x20 bit 5 | Read-only. Loaded from EEPROM. When set, disables ECC generation and error correction.                                                                                                                         |

| ECC CSR access enable   | 17     | 1                                          | When set, enable ECC generation and error correction on CSR access to the Packet Buffer.                                                                                                                       |

| Reserved                | 16     | 1                                          | Reserved. Write to 1                                                                                                                                                                                           |

| ECC error address       | 15:4   | 0xFFF                                      | Contains the Packet Buffer address of the most recent<br>ECC error. Out of reset this is set 0xfff (invalid value)<br>Also set to 0xfff by writing to bit 1 of this register.<br>This field is for Debug only. |

| Reserved                | 3      | 0                                          | Reserved. Write to 0                                                                                                                                                                                           |

| ECC interrupt enable    | 2      | 0                                          | When set, enables the setting of ICR bit 5 on detection of an ECC error                                                                                                                                        |

#### 82571/82572 Specification Update

| ECC Statistic Clear   | 1 | Writing 1 to this bit clears the error counter and error address fields                                          |

|-----------------------|---|------------------------------------------------------------------------------------------------------------------|

| ECC Correction Enable | 0 | When set, enables single bit ECC error correction. When<br>clear, ECC errors will be detected, but not corrected |

### 7. Errata

### 1. When Two Functions Have Differing MAX\_PAYLOAD\_SIZE, the Device Might Use the Larger Value For All Functions.

- Problem: MAX\_PAYLOAD\_SIZE is programmed per function. If two PCIe functions have different MAX\_PAYLOAD\_SIZE, the device might use the larger value for all functions. The usage model for the device is to have all functions use the same MAX\_PAYLOAD\_SIZE.

- Implication: There is no impact on the functional flow.

- Workaround: None.

Status: No Fix: There are no plans to fix this erratum.

#### 2. Upstream Attempt to Reconfigure the PCIe Link By Moving the Link Training Status State Machine (LTSSM) From Recovery to Configuration Will Cause a "Link Down" Event.

- Problem: The device will not move its LTSSM from Recovery to Configuration when it receives Training Sequences (TS) with only "lane number" set to PAD.

- Implication: If the upstream component tries to reconfigure the link by moving the LTSSM from the Recovery.Idle state to the Configuration state (sending TS1s with only "lane number" set to PAD), the link will fail and the units will go to Detect states, causing a "link down" event.

- Workaround: The upstream component should not apply this option.

Status: No Fix: There are no plans to fix this erratum.

### 3. When Using Serial Over LAN, the Device's Power State Can Be Ambiguous.

- Problem: The same physical line is allocated for SMBus Alert and for S0 Power Indication. In Serial-Over-LAN (SOL), both are needed by manageability firmware, which treats these indications as separate. For LOMs containing SOL, the line is used for SMBus Alert.

- Implication: There are two implications:

- SOL behavior might be confused because an SMBus Alert might be considered as a power state indication

- SOL cannot ascertain when a power state change has occurred

Workaround: None.

Status: No Fix: There are no plans to fix this erratum.

#### 4. PCIe Differential- and Common-Mode Return Loss Is Higher Than Specified Value.

Problem: The PCIe transmitter's differential return loss is up to -9 dB instead of the -10 dB requirement. A PCIe Engineering Change Notice sets -10 dB as the requirement instead of the previous -15 dB in the base 1.0a specification..

The PCIe receiver's worst-measured differential return loss is up to -7.7dB instead of the -10dB requirement.

Implication: The out-of-specification return loss adds noise to the TX transmission line.

Workaround: None.

Status: No Fix: There are no plans to fix this erratum.

### 5. SerDes Transmit Differential Return Loss Is Higher Than Specified Value.

- Problem: The SerDes transmitter's differential return loss is up to -9 dB instead of the -10 dB requirement. A PCIe Engineering Change Notice sets -10 dB as the requirement instead of the previous -15 dB in the base 1.0a specification..

- Implication: The out-of-specification return loss adds noise to the TX transmission line.

- Workaround: None.

Status: No Fix: There are no plans to fix this erratum.

### 6. SerDes Is Unable to Acquire Sync from Ordered Sets Beginning with /K28.1/.

- Problem: Device SerDes is unable to acquire sync from ordered sets beginning with /K28.1/. If the link partner did not transmit any other characters that contain "commas" other than /K28.1/, the device will not attain sync.

- Implication: Artificial testing of this portion of the standard will produce failures.

Workaround: None.

Status: No Fix: There are no plans to fix this erratum.

### 7. Device Transmit Operation Might Halt in TCP Segmentation Offload (TSO) Mode when Multiple Requests (MULR) Are Enabled.

- Problem The Device Transmit flow stops and the device hangs when operating in TSO with MULR enabled.

- Implication: When operating in TCP Segmentation Offload mode and with Multiple Request enabled, one of the two workarounds listed below must be in place, or the Transmit Flow will stop unexpectedly.

- Workaround: The driver must ensure that the first descriptor points to the (L2+L3+L4) Header and at least two bytes of the data (payload). This has been implemented in the Intel drivers. This workaround must be applied before activating TSO when MULR=1.

Alternatively, register 0x3940 "TARC1" bit 22 can be set at initialization time to workaround this issue.

Status: No Fix: There are no plans to fix this erratum.

### 8. IDE-Redirect Persistent Retransmission Inconsistency.

- Problem: When sending the "StartIDERedirection" message from a remote management console, a "NumRetransmits" value of zero should define a persistent retransmission of "StartIDERedirection" messages until link is achieved. The device transmits only one "StartIDERedirection" message.

- Implication: Using the value of zero is equivalent to using the value of one.

- Workaround: Use a numeric value of NumRetransmits that is not zero or one.

- Status: No Fix: There are no plans to fix this erratum.

### 9. SMBus Transactions Might Be NACKed (Not ACKnowledged) under IDE and SMBus Stress.

- Problem: IDE and SMBus stress might cause a small percentage (<0.05%) of SMBus transactions to be NACKed. This is due to speed and memory limitations.

- Implication: NACKing SMBus transactions does not impact function.

- Workaround: Not applicable.

- Status: No Fix: There are no plans to fix this erratum.

### **10.** I<sup>2</sup>C Transactions: When Working with Bus Speeds 400 KHz or Higher, the Bus Might Hang When the Master Reads More Bytes than the Slave Reported.

- Problem: When working in  $I^2C$  mode, and when BMC executes an  $I^2C$  read transaction, the device responds with a block of data in which the first returned byte indicates data-length. If the BMC attempts to read more bytes than specified by the data-length byte, a bus hang may occur.

- Implication: If the BMC, operating in I2C mode, reads slave data disregarding the data-length, it will cause the bus to hang.

- Workaround: When BMC acts as Master, it should interpret the first returned data byte received from the device as data-length, and should stop the transaction after reading the specified number of bytes.

- Status: No Fix: There are no plans to fix this erratum.

### **11.** SOL Timeout Character Control Byte In EEPROM Image Does Not Function.

- Problem: SOL (serial over lan) character control can be configured from the EEPROM. Packets from the host to the management console will be sent when either the maximum buffer size or a timeout are reached. However, instead of restarting the timer on every transmit to LAN; the timer is restarted every time a new character arrives from the host. When the transmit rate from the host is slow, the characters will only be sent when the buffer threshold is reached.

- Implication: Characters transmitted from the host may not arrive at the remote console at the expected refresh rate, but in bursts. This will usually be noticed only at slow rates (for example, manual typing), which is not a use case in SOL.

- Workaround: None.

- Status: No Fix: There are no plans to fix this erratum.

### **12.** Incorrect Number of Retransmissions of Link-Down Alert.

- Problem: In ASF mode, if Register EEh (Link up delay) is set to 0, then the number of Link Loss packets that are transmitted is one less than the number set in the ASF register EBh.

Implication: The number of Link Loss packets that are transmitted is one less than the desired number.

Workaround: Set Link up delay to 1, or set retransmission number to be one more than the required retransmission number.

- Status: No Fix: There are no plans to fix this erratum.

### 13. Device Does Not Support PCIe Active State Power Management L1 State (ASPM L1).

Problem: When the device is in ASPM L1, the dynamic clock gating mode is active as a powersaving feature. In this instance, the activating condition for dynamic clock gating is erroneous, resulting in the DMA clock halting when it should be operating.

When both ASPM L1 and ASPM L0 are enabled, and the PCIe interface is set to the x1 mode, the device might cause the PCIe interface to stop responding during the ASPM L1 entry handshake.

Implication: While the device is in ASPM L1 mode, the DMA clock is halted, thus an initiated LSC (Link Status Change) interrupt will be held until the clock is restarted.

While the device is at ASPM L1, and a single packet is received, the packet will be fully DMA'd to the host, but the clock may halt before the write-back is finished, resulting in packet loss.

ASPM L1 must not be enabled.

Workaround: Disable ASPM L1; a device connected to I/O Control Hub 7 (ICH7). Disabling ASPM L1 will prevent the DMI link between ICH7 and the Memory Control Hub (MCH) from entering ASPM L1.

Disable Dynamic Clock gating; this is controlled by EEPROM Word 0xF bit 3. This bit should be always be set to 0 when ASPM is used. EEPROM images based on dev\_starter image 5.6 or older have this bit enabled. EEPROM images based on dev\_starter image 5.7 or later have this disabled by default.

Advertise ASPM L0s support only; ensure bits 3:2 in Word 0x 1A are set to b01. EEPROM images based on dev\_starter image 5.6 or older have these bits set to advertise to the system that ASPM L1 is supported in the device. EEPROM images based on dev\_starter image 5.7 or later do not advertise ASPM L1 support. Please note the system decides whether to put the device in ASPM L1

Status: No Fix: There are no plans to fix this erratum.

### 14. XOFF from Partner Can Prevent Flow-Control (XON/XOFF) Transmission.

Problem: When the device transmitter is paused (by reception of an XOFF packet from the link partner) while data is being processed to be transmitted, both the transmission of normal packets and the outbound XON/XOFF frames (resulting from Receive Packets Buffer level and Flow-Control Thresholds) are paused. Normally, the link partner's XOFF packets pauses the LAN controller for a finite time interval, after which outbound XON/ XOFF's (due to the Receives-PacketBuffer being full) can be sent again. Implication: If the transmitter is paused and the receive FIFO XOFF threshold is reached, the transmission of the XOFF frame does not occur and the Receive FIFO overrun may potentially occur, resulting in lost packets. This is only expected to be seen with an abnormally high pause time from link partners XOFF packet(s). Workaround: To minimize the likelihood of a Receive FIFO overrun, Receive Flow-Control Thresholds should be based on the expected maximum pause interval in the link partner's XOFF packet. This has been implemented in the Intel drivers.

Status: No Fix: There are no plans to fix this erratum.

#### **15. Missed RX Packets.**

- When the device operates with multiple-requests or Large Send enabled, there could be Problem: receive packet loss. When the Tx FIFO is full, the Tx flow may block the host DMA interface of the device. When the transmission of packets is prevented for a long time, due to capture effect or very long backoff in half-duplex, the transmit FIFO is filled and the fetch of Rx descriptors is prevented also. This will prevent the release of the packets from the Rx FIFO to the host, causing the Rx buffer to overflow and the loss of incoming packets. This is a temporary state that will be released once the transmit side is be able to empty the Tx packet buffer. There could be some packet loss in the Rx path if the transmission of packets is Implication: prevented for a long time. Normally, if this occurs, these packets will be re-transmitted by upper-layer protocols. Workaround: None

- Status: No Fix: There are no plans to fix this erratum.

### 16. Tx Stops During Host Management Stress in 10 Mbps Half-Duplex.

- Problem: When the device operates in 10 Mbps Half-Duplex and a packet from management is involved in excessive collisions while both HOST and MNG have a packet ready in the Tx pipe, the Tx process could get into an abnormal state resulting in Tx sticking.

- Implication: This was found in an abnormal use condition when activating IDE-R together with host stress traffic. In normal operating mode, this condition was not seen.

- Workaround: The "transmit stuck" state will be released by a software reset.

- Status: No Fix: There are no plans to fix this erratum.

### **17.** Device Overwrites Port A LAA to Default Value Due to Port B Software Reset.

- Problem: When the LAA (local administrated address) is set by the driver on one port and the second port driver initiates resets, the LAA on the first port also gets resets and the default MAC address is loaded from the EEPROM.

- Implication: The driver on the second port is not aware to the fact that its LAA was changed and packets addressed to the LAA will be lost.

- Workarounds: When using LAA, the driver should set an additional MAC Address filter (for example, RAR[1]) to the LAA value, so if RAR[0] is overwritten, incoming packets will be accepted by the additional filter. In addition, the driver should poll the value of RAR[0], and, if it detects the RAR[0] value is reset to the EEPROM value, it should reload it with the correct LAA value.

Still, with this workaround the WoL magic packet may not work if a port (for example, port 1) that is enabled for WoL uses a LAA. The problematic scenario is when Port 1 goes to D3 state after checking that it's RAR[0] value is correct. Port 0 goes to D3 state and performs reset for its port, causing the Port 1 LAA to be overwritten again. The port 1 driver is already down, so it does not know this and cannot update this again. As the magic packet WoL uses RAR[0] only, magic packets to port 0 will not wake up the system.

This has been implemented in the Intel drivers.

The following information shows how the workaround can be implemented:

- A boolean flag named *laa\_is\_present* is added to the adapter structure to identify to the driver that the workaround is to be applied.

- struct e1000\_hw {

boolean\_t laa\_is\_present;

• When the driver changes the local MAC address, *laa\_is\_present* is set, if using an 82571, and the new MAC address is written to a redundant slot in the receive address table. In this example, entry 14 is used. Entry 15 should not be used as it may be used by the management functions. In this example, e1000\_rar\_set() is a shared code function used to update the RAR registers.

/\* With 82571 controllers, LAA may be overwritten (with the default)

- \* due to controller reset from the other port. \*/

- if (adapter->hw.mac\_type == e1000\_82571) {

- /\* activate the work around \*/

adapter->hw.laa\_is\_present = 1;

/\* Hold a copy of the LAA in RAR[14] This is done so that

- \* between the time RAR[0] gets clobbered and the time it

- \* gets fixed (in e1000\_watchdog), the actual LAA is in one

- \* of the RARs and no incoming packets directed to this port

- \* are dropped. Eventaully the LAA will be in RAR[0] and

- \* RAR[14] \*/

e1000\_rar\_set(&adapter->hw, adapter->hw.mac\_addr,

E1000\_RAR\_ENTRIES - 1);

- Periodically, for example in the drivers watchdog function, RAR(0) should be updated with the changed LAA as it may have been rewritten by a reset on Port B.

- /\* With 82571 controllers, LAA may be overwritten due to controller

- $^{\star}$  reset from the other port. Set the appropriate LAA in RAR[0]  $^{\star/}$

- if (adapter->hw.mac\_type == e1000\_82571 && adapter->hw.laa\_is\_present)

- e1000\_rar\_set(&adapter->hw, adapter->hw.mac\_addr, 0);

Intel drivers share some common functions, which have been adapted to this issue:

- e1000\_rar\_set() is used to update the RAR registers. No changes are required to adapt to this issue, but it is the function used by the following functions.

- e1000\_init\_rx\_addrs() is used to initialize the receive address registers by updating RAR(0) and clearing the remaining RARs. It has been adapted to reserve a spot for the redundant LAA.

```

void

e1000 init rx addrs(struct e1000 hw *hw)

{

uint32_t i;

uint32 t rar num;

/* Setup the receive address. */

e1000_rar_set(hw, hw->mac_addr, 0);

rar num = E1000 RAR ENTRIES;

/* Reserve a spot for the Locally Administered Address to work around

* an 82571 issue in which a reset on one port will reload the MAC on

* the other port. */

if ((hw->mac_type == e1000_82571) && (hw->laa_is_present == TRUE))

rar num -= 1;

/* Zero out the other 15 receive addresses. */

for(i = 1; i < rar num; i++) {

E1000 WRITE REG ARRAY(hw, RA, (i \le 1), 0);

E1000_WRITE_REG_ARRAY(hw, RA, ((i << 1) + 1), 0);

}

}

```

• e1000\_mc\_addr\_list\_update() is used to initialize the multicast address registers and the receive address registers. It has been adapted to reserve a spot for the redundant LAA.

uint32\_t num\_rar\_entry;

uint32\_t num\_mta\_entry;

/\* Set the new number of MC addresses that we are being requested to use. \*/ hw->num\_mc\_addrs = mc\_addr\_count;

```

/* Clear RAR[1-15] */

num_rar_entry = E1000_RAR_ENTRIES;

/* Reserve a spot for the Locally Administered Address to work around

* an 82571 issue in which a reset on one port will reload the MAC on

* the other port. */

if ((hw->mac_type == e1000_82571) && (hw->laa_is_present == TRUE))

num_rar_entry -= 1;

for(i = rar_used_count; i < num_rar_entry; i++) {</pre>

E1000 WRITE REG ARRAY(hw, RA, (i \le 1), 0);

E1000_WRITE_REG_ARRAY(hw, RA, ((i << 1) + 1), 0);

}

/* Clear the MTA */

num mta entry = E1000 NUM MTA REGISTERS;

for(i = 0; i < num_mta_entry; i++) {</pre>

E1000_WRITE_REG_ARRAY(hw, MTA, i, 0);

}

/* Add the new addresses */

for(i = 0; i < mc_addr_count; i++) {

hash_value = e1000_hash_mc_addr(hw,

mc addr list +

(i * (ETH_LENGTH_OF_ADDRESS + pad)));

/* Place this multicast address in the RAR if there is room, *

* else put it in the MTA

*/

if (rar_used_count < num_rar_entry) {</pre>

e1000 rar set(hw,

mc_addr_list + (i * (ETH_LENGTH_OF_ADDRESS + pad)),

rar_used_count);

rar_used_count++;

} else {

e1000_mta_set(hw, hash_value);

}

}

}

```

# **18.** Enabling Or Disabling RSS in the Middle of Received Packets May Stop Receive Flow.

- Problem: Enabling RSS consists of setting both the Multiple Receive Queues Enable bit in MRQC and the Packet Checksum Disable bit in RXCSUM. Changing these settings while there is data in the receive data FIFO could cause the receive DMA to hang. There may be data present in the receive data FIFO even before the driver initialization is executed if the manageability firmware routes some packets to the host using MANC2H.

- Implication: No data received.

Workaround: The driver should implement the following sequence during initialization if RSS is used:

- Set PBS[31] to disable the receive FIFO.

- Perform a software reset to clear the receive FIFO.

- Set up RSS.

- Write RDFHS = (PBA[5:0] << 7) 1

- Clear PBS[31].

- Clear RDFHS.

- Set RCTL.EN to enable packet reception

Status: No Fix: There are no plans to fix this erratum.

### **19.** Packets with IPV6 Tunneled in IPV4 and with a Certain Value of Last IP Options Will Have an Incorrect RSS Hash Value.

- Problem: When IPV6-tunneled-in-IPV4 packets are received, IP option with data is present, and the last byte of IP option is 0x08, an incorrect value of RSS hash (it will be 0x0), queue, and CPU numbers may be calculated.

- Implication: When working with RSS, the platform uses the RSS hash to do TCP context lookup and has no way of recovering if the RSS hash value is incorrect. In this case, it will drop the packet, and possibly reset the connection.

In addition, this packet may be directed to a wrong queue and wrong CPU.

Workaround: If RSS hash value is 0 and PKTTYPE = 3, 4, 9 or 0xA, check IP length. If options are present, do not indicate an RSS hash value to the stack. The TCP stack will calculate the RSS hash value for a TCP packet, which will prevent it from being dropped.

This has been implemented in the Intel drivers.

Status: No Fix: There are no plans to fix this erratum.

### **20.** Formed and Invalid /C/ Code Handling on the SerDes Interface.

Problem: The device responds improperly to certain invalid sequences on the SerDes interface, which include comma characters different than k28.5 or symbols with inverted disparity.

Implication: The device may:

- Achieve link when it shouldn't

- May not restart auto-negotiation when it should

• In normal operation the comma used is k28.5; inverted disparity should not happen on a normal system.

Workaround: None.

Status: No Fix: There are no plans to fix this erratum.

# 21. False Detection of an idle\_match Condition on the SerDes Interface.

Problem:The idle\_match function is used during the auto-negotiation process for 1000 BASE-X<br/>applications (SerDes). This function continuously indicates whether three consecutive /<br/>I/ ordered sets have been received and it is observed when moving from IDLE\_DETECT<br/>state to LINK\_OK state within the auto-negotiation state machine.Though there are not three consistent /I/ symbols (that is,. there is some combination<br/>of /I/ and other symbols), the device can incorrectly set the idle match to true.Implication:This failure should not be seen in normal-use cases where there are many consecutive<br/>/I/ symbols in the auto-negotiation process. However, if the erroneous case occurs, the<br/>auto-negotiation will continue and lock on the next /I/ pattern.

Workaround: None

Status: No Fix: There are no plans to fix this erratum.

### 22. Ability Match and Acknowledge Match on the SerDes Interface.