# DS1245Y/AB 1024k Nonvolatile SRAM

### www.maxim-ic.com

#### **FEATURES**

- 10 years minimum data retention in the absence of external power

- Data is automatically protected during power loss

- Replaces 128k x 8 volatile static RAM, EEPROM or Flash memory

- Unlimited write cycles

- Low-power CMOS

- Read and write access times of 70 ns

- Lithium energy source is electrically disconnected to retain freshness until power is applied for the first time

- Full  $\pm 10\%$  V<sub>CC</sub> operating range (DS1245Y)

- Optional ±5% V<sub>CC</sub> operating range (DS1245AB)

- Optional industrial temperature range of -40°C to +85°C, designated IND

- JEDEC standard 32-pin DIP package

- PowerCap Module (PCM) package

- Directly surface-mountable module

- Replaceable snap-on PowerCap provides lithium backup battery

- Standardized pinout for all nonvolatile SRAM products

- Detachment feature on PowerCap allows easy removal using a regular screwdriver

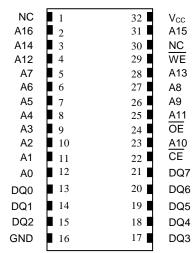

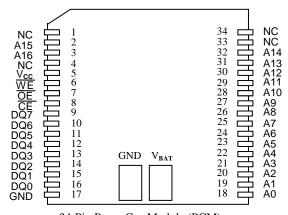

### PIN ASSIGNMENT

32-Pin Encapsulated Package 740-mil Extended

34-Pin PowerCap Module (PCM) (Uses DS9034PC+ or DS9034PCI+ PowerCap)

### PIN DESCRIPTION

A0 - A16 - Address Inputs DQ0 - DQ7 - Data In/Data Out CE - Chip Enable WE - Write Enable <del>OE</del> - Output Enable - Power (+5V) $V_{CC}$ - Ground **GND** NC - No Connect

# **DESCRIPTION**

The DS1245 1024k Nonvolatile SRAMs are 1,048,576-bit, fully static, nonvolatile SRAMs organized as 131,072 words by 8 bits. Each complete NV SRAM has a self-contained lithium energy source and control circuitry which constantly monitors  $V_{CC}$  for an out-of-tolerance condition. When such a condition occurs, the lithium energy source is automatically switched on and write protection is unconditionally enabled to prevent data corruption. DIP-package DS1245 devices can be used in place of existing 128k x 8 static RAMs directly conforming to the popular bytewide 32-pin DIP standard. DS1245 devices in the PowerCap Module package are directly surface mountable and are normally paired with a DS9034PC PowerCap to form a complete Nonvolatile SRAM module. There is no limit on the number of write cycles that can be executed and no additional support circuitry is required for microprocessor interfacing.

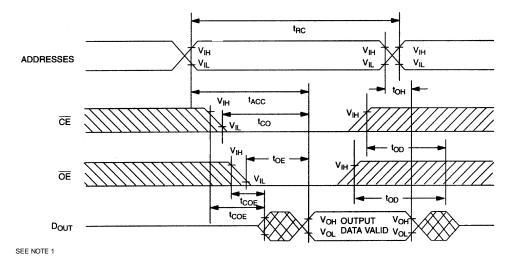

## **READ MODE**

The DS1245 executes a read cycle whenever  $\overline{WE}$  (Write Enable) is inactive (high) and  $\overline{CE}$  (Chip Enable) and  $\overline{OE}$  (Output Enable) are active (low). The unique address specified by the 17 address inputs (A<sub>0</sub> - A<sub>16</sub>) defines which of the 131,072 bytes of data is to be accessed. Valid data will be available to the eight data output drivers within  $t_{ACC}$  (Access Time) after the last address input signal is stable, providing that  $\overline{CE}$  and  $\overline{OE}$  (Output Enable) access times are also satisfied. If  $\overline{OE}$  and  $\overline{CE}$  access times are not satisfied, then data access must be measured from the later occurring signal ( $\overline{CE}$  or  $\overline{OE}$ ) and the limiting parameter is either  $t_{CO}$  for  $\overline{CE}$  or  $t_{OE}$  for  $\overline{OE}$  rather than address access.

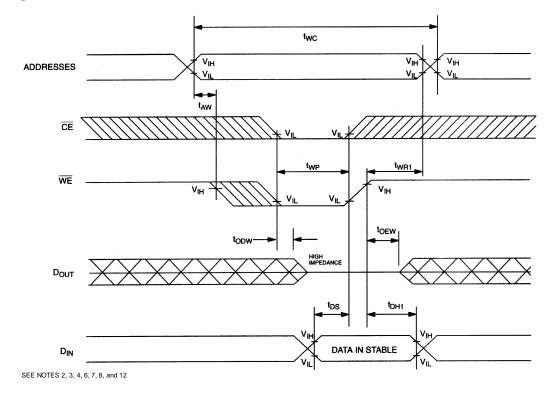

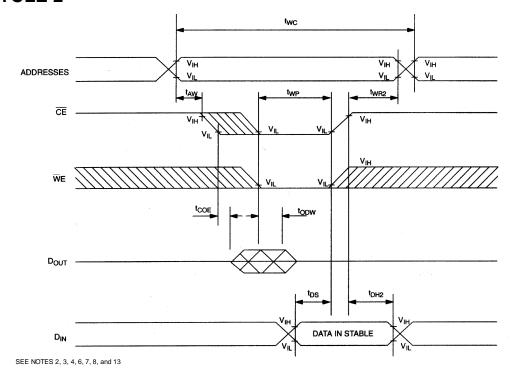

### **WRITE MODE**

The DS1245 executes a write cycle whenever the  $\overline{WE}$  and  $\overline{CE}$  signals are active (low) after address inputs are stable. The later occurring falling edge of  $\overline{CE}$  or  $\overline{WE}$  will determine the start of the write cycle. The write cycle is terminated by the earlier rising edge of  $\overline{CE}$  or  $\overline{WE}$ . All address inputs must be kept valid throughout the write cycle.  $\overline{WE}$  must return to the high state for a minimum recovery time ( $t_{WR}$ ) before another cycle can be initiated. The  $\overline{OE}$  control signal should be kept inactive (high) during write cycles to avoid bus contention. However, if the output drivers are enabled ( $\overline{CE}$  and  $\overline{OE}$  active) then  $\overline{WE}$  will disable the outputs in  $t_{ODW}$  from its falling edge.

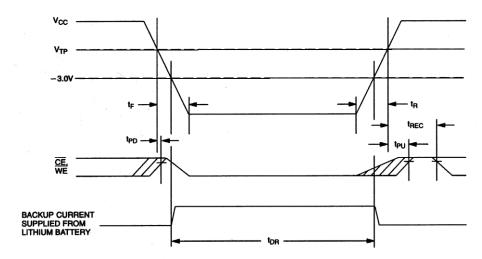

#### DATA RETENTION MODE

The DS1245AB provides full functional capability for  $V_{CC}$  greater than 4.75 volts and write protects by 4.5 volts. The DS1245Y provides full functional capability for  $V_{CC}$  greater than 4.5 volts and write-protects by 4.25 volts. Data is maintained in the absence of  $V_{CC}$  without any additional support circuitry. The nonvolatile static RAMs constantly monitor  $V_{CC}$ . Should the supply voltage decay, the NV SRAMs automatically write-protect themselves, all inputs become "don't care," and all outputs become high impedance. As  $V_{CC}$  falls below approximately 3.0 volts, a power switching circuit connects the lithium energy source to RAM to retain data. During power-up, when  $V_{CC}$  rises above approximately 3.0 volts, the power switching circuit connects external  $V_{CC}$  to RAM and disconnects the lithium energy source. Normal RAM operation can resume after  $V_{CC}$  exceeds 4.75 volts for the DS1245AB and 4.5 volts for the DS1245Y.

#### FRESHNESS SEAL

Each DS1245 device is shipped from Maxim with its lithium energy source disconnected, guaranteeing full energy capacity. When  $V_{\rm CC}$  is first applied at a level greater than 4.25 volts, the lithium energy source is enabled for battery back-up operation.

# **PACKAGES**

The DS1245 devices are available in two packages: 32-pin DIP and 34-pin PowerCap Module (PCM). The 32-pin DIP integrates a lithium battery, an SRAM memory and a nonvolatile control function into a single package with a JEDEC-standard 600-mil DIP pinout. The 34-pin PowerCap Module integrates SRAM memory and nonvolatile control along with contacts for connection to the lithium battery in the DS9034PC PowerCap. The PowerCap Module package design allows a DS1245 PCM device to be surface mounted without subjecting its lithium backup battery to destructive high-temperature reflow soldering. After a DS1245 PCM is reflow soldered, a DS9034PC PowerCap is snapped on top of the PCM to form a complete Nonvolatile SRAM module. The DS9034PC is keyed to prevent improper attachment. DS1245 PowerCap Modules and DS9034PC PowerCaps are ordered separately and shipped in separate containers. See the DS9034PC data sheet for further information.

# **ABSOLUTE MAXIMUM RATINGS**

Voltage on Any Pin Relative to Ground -0.3V to +6.0V

Operating Temperature Range

Commercial:  $0^{\circ}\text{C to } +70^{\circ}\text{C}$

Industrial:  $-40^{\circ}\text{C to } +85^{\circ}\text{C}$

Storage Temperature Range

EDIP  $-40^{\circ}\text{C to } +85^{\circ}\text{C}$

PowerCap -55°C to +125°C

Lead Temperature (soldering, 10s) +260°C

Soldering Temperature (reflow, PowerCap) +260°C

**Note:** EDIP is wave or hand soldered only.

This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# RECOMMENDED DC OPERATING CONDITIONS

(T<sub>A</sub>: See Note 10)

| PARAMETER                     | SYMBOL          | MIN  | TYP | MAX      | UNITS | NOTES |

|-------------------------------|-----------------|------|-----|----------|-------|-------|

| DS1245AB Power Supply Voltage | $V_{CC}$        | 4.75 | 5.0 | 5.25     | V     |       |

| DS1245Y Power Supply Voltage  | $V_{CC}$        | 4.5  | 5.0 | 5.5      | V     |       |

| Logic 1                       | $V_{IH}$        | 2.2  |     | $V_{CC}$ | V     |       |

| Logic 0                       | V <sub>IL</sub> | 0.0  |     | 0.8      | V     |       |

# DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V \pm 5\% \text{ for DS1245AB})$

$(T_A: See Note 10) (V_{CC} = 5V \pm 10\% for DS1245Y)$

| PARAMETER                                                     | SYMBOL     | MIN  | TYP  | MAX  | UNITS | NOTES |

|---------------------------------------------------------------|------------|------|------|------|-------|-------|

| Input Leakage Current                                         | $I_{IL}$   | -1.0 |      | +1.0 | μΑ    |       |

| I/O Leakage Current $\overline{CE} \ge V_{IH} \le V_{CC}$     | $I_{IO}$   | -1.0 |      | +1.0 | μΑ    |       |

| Output Current @ 2.4V                                         | $I_{OH}$   | -1.0 |      |      | mA    |       |

| Output Current @ 0.4V                                         | $I_{OL}$   | 2.0  |      |      | mA    |       |

| Standby Current $\overline{\text{CE}} = 2.2 \text{V}$         | $I_{CCS1}$ |      | 200  | 600  | μΑ    |       |

| Standby Current $\overline{\text{CE}} = V_{\text{CC}} - 0.5V$ | $I_{CCS2}$ |      | 50   | 150  | μΑ    |       |

| Operating Current                                             | $I_{CCO1}$ |      |      | 85   | mA    |       |

| Write Protection Voltage (DS1245AB)                           | $V_{TP}$   | 4.50 | 4.62 | 4.75 | V     |       |

| Write Protection Voltage (DS1245Y)                            | $V_{TP}$   | 4.25 | 4.37 | 4.5  | V     |       |

# **CAPACITANCE** $(T_A = +25^{\circ}C)$

| PARAMETER                | SYMBOL    | MIN | TYP | MAX | UNITS | NOTES |

|--------------------------|-----------|-----|-----|-----|-------|-------|

| Input Capacitance        | $C_{IN}$  |     | 5   | 10  | pF    |       |

| Input/Output Capacitance | $C_{I/O}$ |     | 5   | 10  | pF    |       |

# **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 5V \pm 5\% \text{ for DS1245AB})$

(T<sub>A</sub>: See Note 10) ( $V_{CC} = 5V \pm 10\%$  for DS1245Y)

| PARAMETER                       | SYMBOL                               | DS124   | 5AB-70<br>45Y-70 | UNITS    | NOTES    |  |

|---------------------------------|--------------------------------------|---------|------------------|----------|----------|--|

|                                 |                                      | MIN     | MAX              |          |          |  |

| Read Cycle Time                 | $t_{ m RC}$                          | 70      |                  | ns       |          |  |

| Access Time                     | $t_{ACC}$                            |         | 70               | ns       |          |  |

| OE to Output Valid              | $t_{OE}$                             |         | 35               | ns       |          |  |

| CE to Output Valid              | $t_{\mathrm{CO}}$                    |         | 70               | ns       |          |  |

| OE or CE to Output Active       | $t_{COE}$                            | 5       |                  | ns       | 5        |  |

| Output High Z from Deselection  | t <sub>OD</sub>                      |         | 25               | ns       | 5        |  |

| Output Hold from Address Change | t <sub>OH</sub>                      | 5       |                  | ns       |          |  |

| Write Cycle Time                | $t_{ m WC}$                          | 70      |                  | ns       |          |  |

| Write Pulse Width               | $t_{\mathrm{WP}}$                    | 55      |                  | ns       | 3        |  |

| Address Setup Time              | $t_{AW}$                             | 0       |                  | ns       |          |  |

| Write Recovery Time             | t <sub>WR1</sub><br>t <sub>WR2</sub> | 5<br>15 |                  | ns<br>ns | 12<br>13 |  |

| Output High Z from WE           | $t_{ m ODW}$                         |         | 25               | ns       | 5        |  |

| Output Active from WE           | $t_{OEW}$                            | 5       |                  | ns       | 5        |  |

| Data Setup Time                 | $t_{ m DS}$                          | 30      |                  | ns       | 4        |  |

| Data Hold Time                  | t <sub>DH1</sub><br>t <sub>DH2</sub> | 0<br>10 |                  | ns<br>ns | 12<br>13 |  |

# **READ CYCLE**

# **WRITE CYCLE 1**

# **WRITE CYCLE 2**

# POWER-DOWN/POWER-UP CONDITION

### POWER-DOWN/POWER-UP TIMING

(T<sub>A</sub>: See Note 10)

| PARAMETER                                                            | SYMBOL            | MIN | TYP | MAX | UNITS | NOTES |

|----------------------------------------------------------------------|-------------------|-----|-----|-----|-------|-------|

| $V_{CC}$ Fail Detect to $\overline{CE}$ and $\overline{WE}$ Inactive | $t_{PD}$          |     |     | 1.5 | μs    | 11    |

| V <sub>CC</sub> slew from V <sub>TP</sub> to 0V                      | $t_{\mathrm{F}}$  | 150 |     |     | μs    |       |

| V <sub>CC</sub> slew from 0V to V <sub>TP</sub>                      | $t_R$             | 150 |     |     | μs    |       |

| $V_{CC}$ Valid to $\overline{CE}$ and $\overline{WE}$ Inactive       | $t_{\mathrm{PU}}$ |     |     | 2   | ms    |       |

| V <sub>CC</sub> Valid to End of Write Protection                     | $t_{REC}$         |     |     | 125 | ms    |       |

$(T_A = +25^{\circ}C)$

| PARAMETER                    | SYMBOL   | MIN | TYP | MAX | UNITS | NOTES |

|------------------------------|----------|-----|-----|-----|-------|-------|

| Expected Data Retention Time | $t_{DR}$ | 10  |     |     | years | 9     |

### **WARNING:**

Under no circumstance are negative undershoots, of any amplitude, allowed when device is in battery backup mode.

### NOTES:

- 1.  $\overline{\text{WE}}$  is high for a Read Cycle.

- 2.  $\overline{OE} = V_{IH}$  or  $V_{IL}$ . If  $\overline{OE} = V_{IH}$  during write cycle, the output buffers remain in a high impedance state.

- 3.  $t_{WP}$  is specified as the logical AND of  $\overline{CE}$  and  $\overline{WE}$ .  $t_{WP}$  is measured from the latter of  $\overline{CE}$  or  $\overline{WE}$  going low to the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 4.  $t_{DH}$ ,  $t_{DS}$  are measured from the earlier of  $\overline{CE}$  or  $\overline{WE}$  going high.

- 5. These parameters are sampled with a 5 pF load and are not 100% tested.

- 6. If the  $\overline{\text{CE}}$  low transition occurs simultaneously with or latter than the  $\overline{\text{WE}}$  low transition, the output buffers remain in a high impedance state during this period.

- 7. If the  $\overline{\text{CE}}$  high transition occurs prior to or simultaneously with the  $\overline{\text{WE}}$  high transition, the output buffers remain in high impedance state during this period.

- 8. If  $\overline{\text{WE}}$  is low or the  $\overline{\text{WE}}$  low transition occurs prior to or simultaneously with the  $\overline{\text{CE}}$  low transition, the output buffers remain in a high impedance state during this period.

- 9. Each DS1245 has a built-in switch that disconnects the lithium source until the user first applies V<sub>CC</sub>. The expected t<sub>DR</sub> is defined as accumulative time in the absence of V<sub>CC</sub> starting from the time power is first applied by the user. This parameter is assured by component selection, process control, and design. It is not measured directly during production testing.

- 10. Each DS1245 has a built-in switch that disconnects the lithium source until  $V_{CC}$  is first applied by the user. The expected  $t_{DR}$  is defined as accumulative time in the absence of  $V_{CC}$  starting from the time power is first applied by the user.

- 11. All AC and DC electrical characteristics are valid over the full operating temperature range. For commercial products, this range is 0°C to 70°C. For industrial products (IND), this range is -40°C to +85°C.

- 12. In a power-down condition the voltage on any pin may not exceed the voltage on V<sub>CC</sub>.

- 13.  $t_{WR1}$  and  $t_{DH1}$  are measured from  $\overline{WE}$  going high.

- 14.  $t_{WR2}$  and  $t_{DH2}$  are measured from  $\overline{CE}$  going high.

- 15. DS1245 modules are recognized by Underwriters Laboratories (UL) under file E99151.

### DC TEST CONDITIONS

Outputs Open Cycle = 200 ns for operating current All voltages are referenced to ground

## **AC TEST CONDITIONS**

Output Load: 100 pF + 1TTL Gate Input Pulse Levels: 0 - 3.0V

Timing Measurement Reference Levels

Input: 1.5V Output: 1.5V

Input pulse Rise and Fall Times: 5 ns

### ORDERING INFORMATION

| PART             | TEMP RANGE     | SUPPLY<br>TOLERANCE | PIN-PACKAGE  | SPEED GRADE (ns) |

|------------------|----------------|---------------------|--------------|------------------|

| DS1245AB-70+     | 0°C to +70°C   | 5V ± 5%             | 32 740 EDIP  | 70               |

| DS1245ABP-70+    | 0°C to +70°C   | 5V ± 5%             | 34 PowerCap* | 70               |

| DS1245AB-70IND+  | -40°C to +85°C | 5V ± 5%             | 32 740 EDIP  | 70               |

| DS1245ABP-70IND+ | -40°C to +85°C | 5V ± 5%             | 34 PowerCap* | 70               |

| DS1245Y-70+      | 0°C to +70°C   | 5V ± 10%            | 32 740 EDIP  | 70               |

| DS1245YP-70+     | 0°C to +70°C   | 5V ± 10%            | 34 PowerCap* | 70               |

| DS1245Y-70IND+   | -40°C to +85°C | 5V ± 10%            | 32 740 EDIP  | 70               |

| DS1245YP-70IND+  | -40°C to +85°C | 5V ± 10%            | 34 PowerCap* | 70               |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# PACKAGE INFORMATION

For the latest package outline information and land patterns, go to <a href="www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE TYPE | PACKAGE CODE | OUTLINE NO.    | LAND PATTERN NO. |

|--------------|--------------|----------------|------------------|

| 32 EDIP      | MDT32+6      | <u>21-0245</u> | _                |

| 34 PCAP      | PC2+3        | <u>21-0246</u> | _                |

<sup>\*</sup>DS9034PC+ or DS9034PCI+ (PowerCap) required. Must be ordered separately.

# **REVISION HISTORY**

| REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                     | PAGES<br>CHANGED |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 121907           | Added <i>Package Information</i> table; removed the DIP module package drawing and dimension table                                                                                                                                                                                                                                                                                                                                              | 10, 11, 12       |

| 11/10            | Updated the storage information, soldering temperature, and lead temperature information in the <i>Absolute Maximum Ratings</i> section; removed the -85, -100, and -120 MIN/MAX information from the <i>AC Electrical Characteristics</i> table; updated the <i>Ordering Information</i> table (removed -85, -100, and -120 parts and leaded -70 parts); removed the PowerCap module drawings and updated the <i>Package Information</i> table | 1, 4, 5, 9       |