# Le78D11

# Integrated Voice Chip Sets VE770 Series

#### **APPLICATIONS**

- Ideal for Short/Medium Loops of ~2000 ft, 26 AWG, and 5 REN loads

- Voice over IP/DSL Integrated Access Devices, Smart Residential Gateways, Home Gateway/Router

- Cable Telephony NIU, Set-Top Box, Home Side Box, Cable Modem, Cable PC

- Fiber–Fiber in the Loop (FITL), Fiber to the Home (FTTH)

- Wireless Local Loop, Intelligent PBX, ISDN NT1/TA

#### **FEATURES**

- Integrated Dual-Channel Chipset

- Switching regulator support

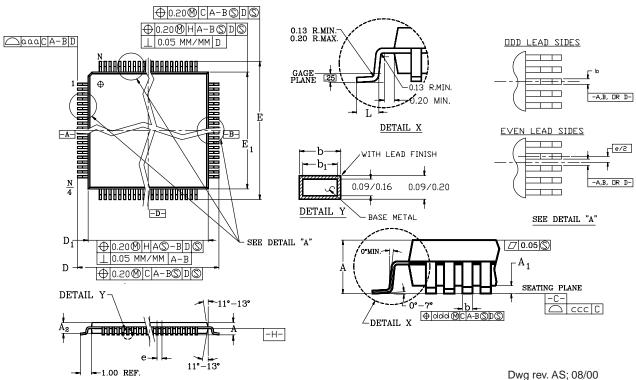

- 44-pin TQFP Package

- 3.3 V Operation

- Subscriber Loop Test/Self-Test

- GR-909 compliant drop test capability in both measurements and pass/fail

- Hazardous Potential

- Foreign Electromotive Force

- Resistive Faults

- Receive off-hook

- Ringers Test

- Loop length

- Real-time automatic line fault detection & reporting

- Loop Supervision

- AC/DC Faults

- Integrated self tests

- Loopback tests

- Checksum of programmed values

- µ-law, A-law, ADPCM or linear coding

- Industry Standard Interfaces

- PCM/SPI or GCI

- World Wide programmability:

- Ringing waveform generation and control

- Two-wire AC impedance

- Trans-hybrid balance with Adaptation

- Gain

- Programmable loop closure/ringtrip thresholds

- Metering Tone Generation

- Call Progress Tones

- DTMF Generation AND Detection

- FSK/Caller ID Tone Generation -Type I, Type II, & worldwide

- Modem/Fax Tone Detection

- Low power dissipation

#### RELATED LITERATURE

- 080696 Le77D11 VoSLIC™ Device Data Sheet

- 080716 Le77D11 /Le78D11 Chip Set User's Guide

- 081081 Le71HE0011 Evaluation Board User's Guide

- 080729 VoicePath™ API Software Product Brief

- 080727 WinSLAC™ Software Product Brief

#### ORDERING INFORMATION

A Legerity VoSLIC™ device must be used with this part.

| Device      | Package                      |

|-------------|------------------------------|

| LE78D110VC  | 44-pin TQFP                  |

| LE78D110BVC | 44-pin TQFP (Green package)* |

\*Green package meets RoHS Directive 2002/95/EC of the European Council to minimize the environmental impact of electrical equipment.

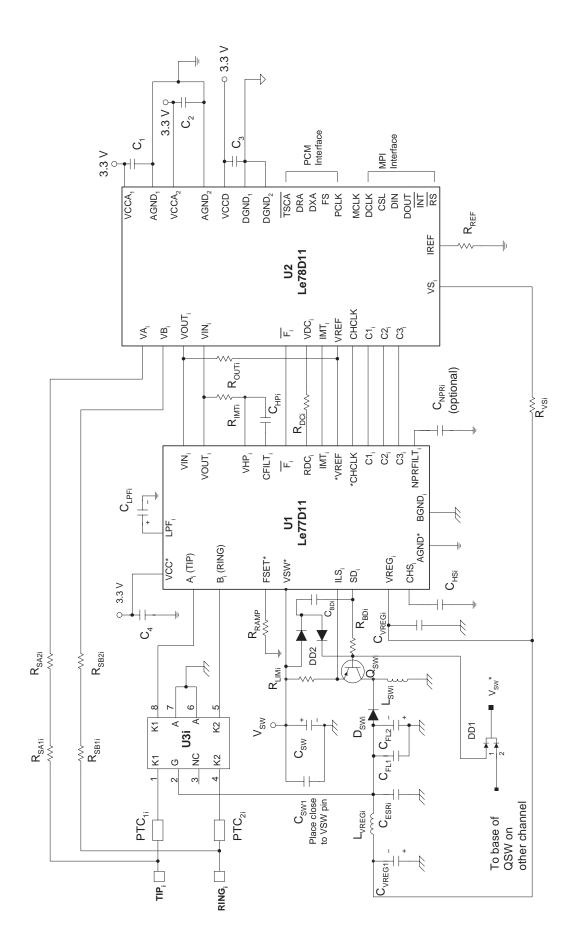

### **DESCRIPTION**

Legerity's Le78D11 VoSLAC™ device has enhanced and optimized features to directly address the requirements of Voice over Broadband (VoB) applications. Their common goal is to reduce system level cost, board space, and power through higher levels of integration. In addition, this solution reduces the total cost of ownership of the end product by promoting higher quality of service through integrated line and self test capabilities. The VE770 series chip set uses two devices to provide a completely software configurable solution to perform the BORSCHT functions for two lines, including provision of a single line battery voltage. The resulting system is less complex, smaller, and denser, yet cost-effective with minimal external components.

Easy integration into the end application is enabled by the VoicePath™ API Software. Written in ANSI "C," the software development kit reduces the complexity of adding voice into a product and makes use of the more sophisticated chip set functions, such as Caller ID. It includes a management tool that works with the WinSLAC™ Coefficient Generator to easily support multiple market applications.

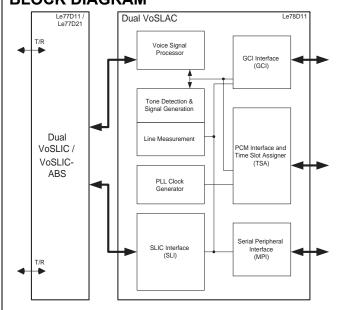

### **BLOCK DIAGRAM**

Document ID#

080697

Date:

Sep 30, 2004

Rev:

D

Version:

1

Distribution:

Public Document

1

# **TABLE OF CONTENTS**

| Applications1                                              |

|------------------------------------------------------------|

| Features                                                   |

| Related Literature                                         |

| Ordering Information                                       |

| Description                                                |

| Block Diagram                                              |

| List of Figures                                            |

| Product Description                                        |

| Block Descriptions                                         |

| PCM Interface and Time Slot Assigner (TSA)                 |

| Microprocessor Interface (MPI)                             |

| General Circuit Interface (GCI) Mode                       |

| PLL Clock Generator                                        |

| SLIC Device Interface (SLI)                                |

| Line Supervision Processing                                |

| Voice Signal Processing                                    |

| Tone Detection and Signal Generation                       |

| Line Measurement                                           |

| Band Gap Voltage Reference                                 |

| Connection Diagram                                         |

| Pin Descriptions                                           |

| Absolute Maximum Ratings                                   |

| Operating Ranges                                           |

|                                                            |

| Environmental Ranges                                       |

| Electrical Maximum Ranges                                  |

| Electrical Characteristics                                 |

| Power Dissipation                                          |

| Specifications                                             |

| System Specifications                                      |

| Device DC Specifications                                   |

| Transmission Specifications                                |

| Transmit and Receive Paths                                 |

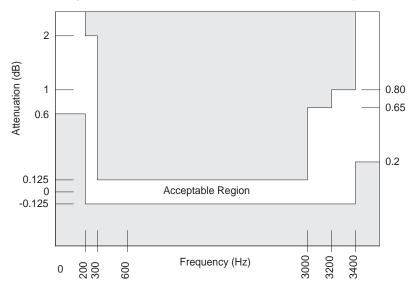

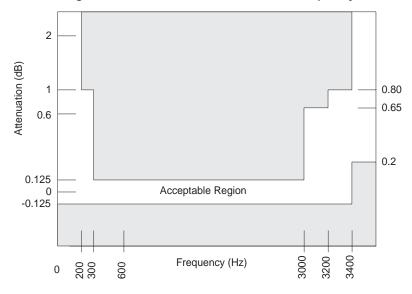

| Attenuation Distortion                                     |

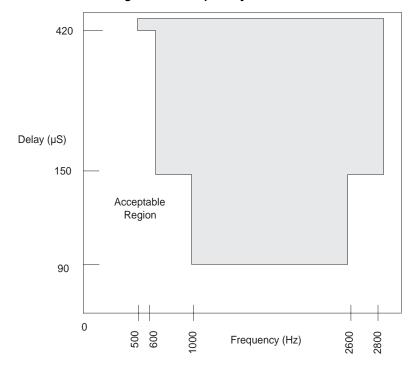

| Group Delay Distortion                                     |

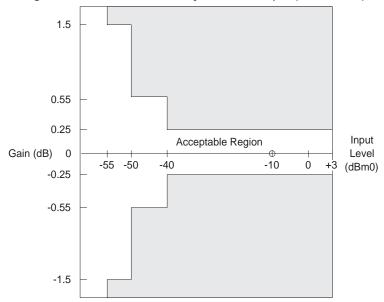

| Gain Linearity                                             |

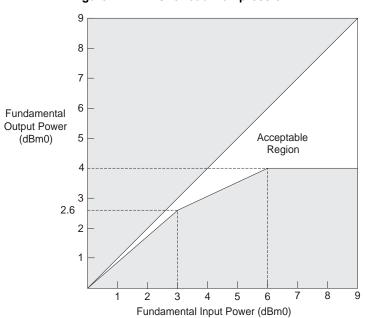

| Overload Compression                                       |

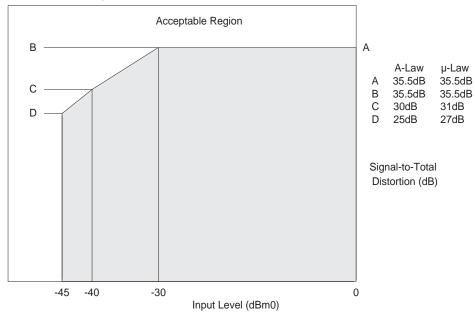

| Total Distortion Including Quantizing Distortion           |

| Single Frequency Distortion                                |

| Intermodulation Distortion                                 |

| Discrimination Against Out-of-Band Input Signals20         |

| Discrimination Against 12- and 16-kHz Metering Signals     |

| Spurious Out-of-Band Signals at the Analog Output          |

| Switching Characteristics                                  |

| Microprocessor Interface                                   |

| PCM Interface                                              |

| Master Clock                                               |

| Chopper Clock                                              |

| GCI Interface                                              |

| Switching Waveforms                                        |

| Single Channel Application Circuit with the Le77D11 Device |

| Application Circuit Parts List for the Le77D11 Device      |

| Physical Dimensions                                        |

| Revision History                                           |

| Revision B1 to C1                                          |

| Revision C1 to D1                                          |

# **LIST OF FIGURES**

| Figure 1.  | Le78D11 VoSLAC™ Device Block Diagram                           |    |

|------------|----------------------------------------------------------------|----|

| Figure 2.  | Transmit Path Attenuation vs. Frequency                        |    |

| Figure 3.  | Receive Path Attenuation vs. Frequency                         |    |

| Figure 4.  | Group Delay Distortion                                         |    |

| Figure 5.  | A-law Gain Linearity with Tone Input (Both Paths)              |    |

| Figure 6.  | μ-law Gain Linearity with Tone Input (Both Paths)              | 19 |

| Figure 7.  | A/A Overload Compression                                       |    |

| Figure 8.  | Total Distortion with Tone Input (Both Paths)                  |    |

| Figure 9.  | Discrimination Against Out-of-Band Signals                     |    |

| Figure 10. | Spurious Out-of-Band Signals                                   |    |

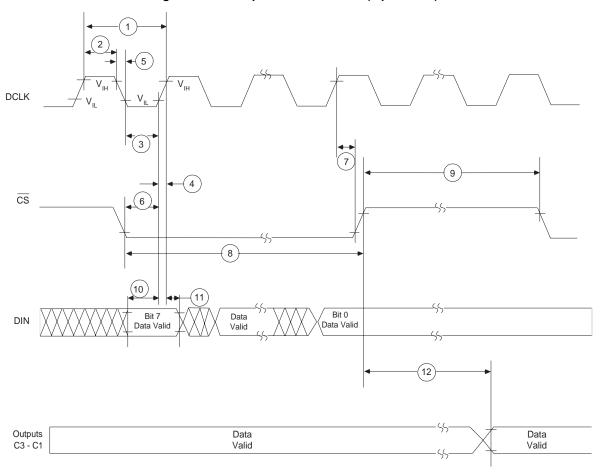

| Figure 11. | Microprocessor Interface (Input Mode)                          |    |

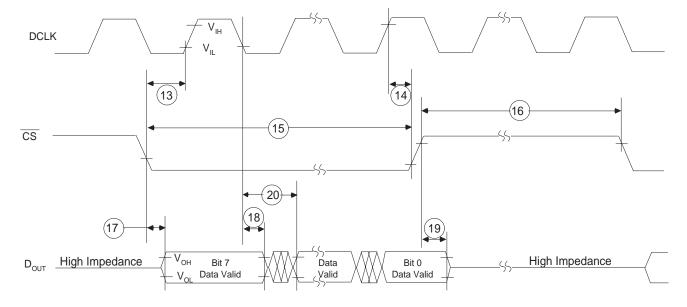

| Figure 12. | Microprocessor Interface (Output Mode)                         |    |

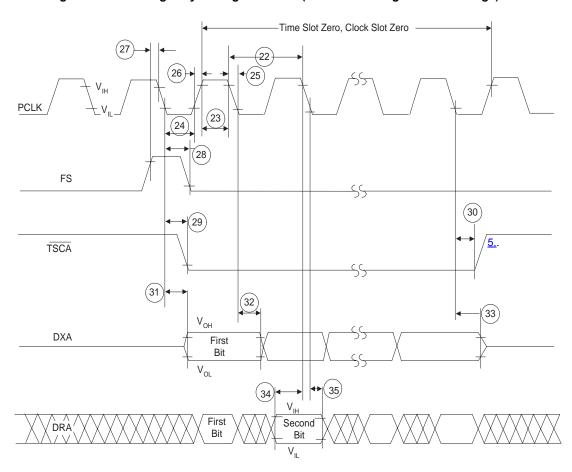

| Figure 13. | PCM Highway Timing for XE = 0 (Transmit on Negative PCLK Edge) |    |

| Figure 14. | PCM Highway Timing for XE = 1 (Transmit on Positive PCLK Edge) |    |

| Figure 15. | Master Clock Timing                                            |    |

| Figure 16. | Chopper Clock Timing                                           |    |

| Figure 17. | Input and Output Waveforms for AC tests                        |    |

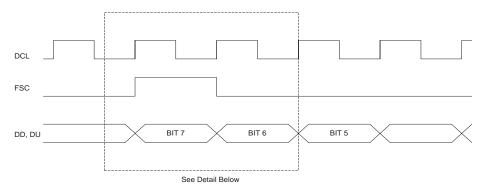

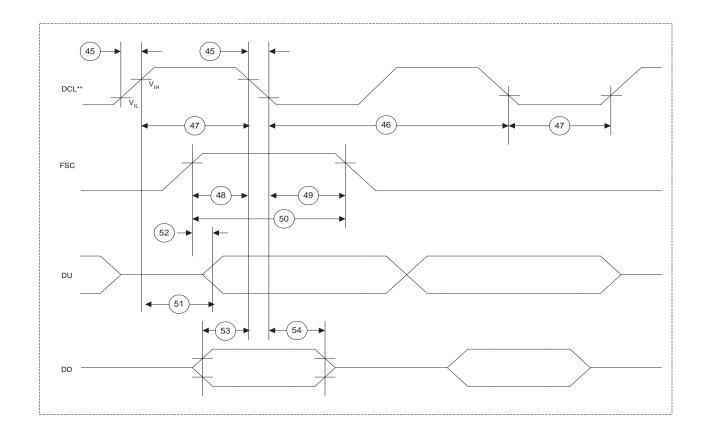

| Figure 18. | 4.096 MHz DCL GCI Operation                                    |    |

| Figure 19. | 2.048 MHz DCL GCI Operation                                    |    |

# PRODUCT DESCRIPTION

The Le78D11 VoSLAC device contains high performance circuits that provide A/D and D/A conversion for two sets of voice (codec), loop supervision, and line diagnostic functions. Fixed function DSP resources in the device are used to perform modem detection, DTMF detection, ADPCM voice compression, and echo cancellation. Although the device offers a high degree of programmability, the available WinSLAC and VoicePath™ software packages allow the user to easily configure and control the Voice Line Circuits (VLC) and the programmable filter coefficients and loop supervision data are easily calculated.

The main functions that can be observed and controlled through the Le78D11 VoSLAC device are:

- Off Hook detection

- · Ring trip detection

- Line Fault Indication

- Ground Key detection

- · DTMF detection

- Fax and Modem tone (1100 Hz and 2100 Hz) detection

- DC Loop Current Limit

- Ring Generation

- Subscriber line impedance matching

- · Metering Signal Generation

- · Line Circuit test

In order for the Le78D11 VoSLAC device to accomplish the above functions, it must receive input from the Legerity Le77D11 devices, which sense the following parameters and scale them appropriately for the Le78D11 VoSLAC device:

- V<sub>IN</sub>: A metallic AC voltage that is proportional to the upstream AC loop current

- I<sub>MT</sub>: A current that is proportional to the DC + AC loop current

- F: A logic Low indicates a fault or ground key condition

The Le78D11 VoSLAC device then outputs the following to the Le77D11 SLIC device:

- V<sub>DC</sub>: DC loop current limit threshold control voltage

- V<sub>OLIT</sub>: Downstream voice and low level metering signals or internal ringing or test signals

The Le78D11 device performs the codec and filter functions associated with the 4-wire section of the subscriber line circuitry in a digital switch. These functions involve converting an analog voice signal into digital PCM samples and converting digital PCM samples back into an analog signal. During conversion, digital filters are used to band-limit the voice signals. The user programmable filters set the receive and transmit gain, perform the transhybrid balancing function, permit adjustment of the 2-wire termination impedance, and provide frequency distortion adjustment (equalization) of the receive and transmit paths. An Adaptive Transhybrid Balance filter is included that allows the Le78D11 VoSLAC device to dynamically adjust to changing line conditions minimizing objectionable echo. All programmable digital filter coefficients can be calculated using WinSLAC software. The PCM codes can be either 16-bit linear two's complement, 8-bit companded A-law or μ-law, or 32 kbit/s or 24 kbit/s ADPCM.

#### **BLOCK DESCRIPTIONS**

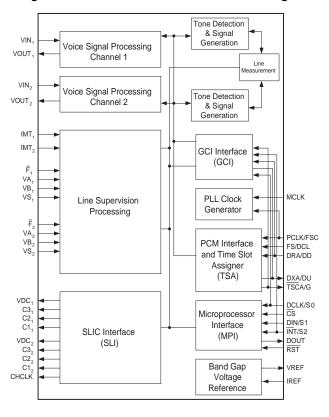

Figure 1. Le78D11 VoSLAC Device Block Diagram

The following provides an overview of the functions of the Le78D11 VoSLAC device. Detailed descriptions and command sets are provided in the *Le77D11/Le78D11 Chip Set User's Guide* (document ID# 080716).

The Le78D11 VoSLAC device supports two digital interface modes: (1) PCM/MPI, where voice and control data are carried over separate serial interfaces, and (2) GCI, where the voice and control data are combined onto a single serial bus. The two modes are exclusive and the associated pins have dual functions. The naming convention for the pins lists the PCM/MPI interface function first then the GCI function.

# PCM Interface and Time Slot Assigner (TSA)

The Le78D11 VoSLAC device powers up in PCM/MPI mode. If a signal is detected on PCLK (PCM Clock) and FS (Frame Sync) is toggling at a slower rate, the PCM interface and time slot assigner functions are maintained. This block uses five signals: PCLK, FS, DXA, DRA and TSCA.

The PCM Interface is a synchronous serial mode of communication between the system and the Le78D11 VoSLAC device for exchanging the encoded voice signals on a "PCM highway". This highway uses FS as a nominally 8kHz synchronization (frame) reference and PCLK as a data strobe that determines the rate at which the data is shifted out of the DXA pin and into the DRA pin. The Le78D11 VoSLAC device transmits/ receives either 8-bits of (A-law/µ-law) compressed voice data, 4bits of 32 kb/s ADPCM data, 3 bits of 24 kb/s ADPCM data, or 16-bits of linear two's complement voice data every frame. The PCLK frequency can be any multiple of the FS frequency from 128 kHz to 8.192 MHz for compressed data, and from 256 kHz to 8.192 MHz for linear data. The position of the data within the frame is controlled by the TSA and determined by a combination of three programmable variables. The first is the Transmit and Receive Clock Slot Register which allows setting from 0 to 7 PCLK periods of clock skew in the system. The second is the XE bit, also in the Transmit and Receive Clock Slot Register, which selects the clock edge used for transmitting or receiving data. Finally, the Transmit and Receive Timeslot Register allows the data for each channel to be offset within a frame by 8 bit increments or timeslots.

### Microprocessor Interface (MPI)

The Le78D11 VoSLAC device Microprocessor Interface (MPI) is used in conjunction with PCM operation. It is a simple synchronous serial interface. It consists of  $\underline{six}$  signals: reset (RST), serial data in (DIN), serial data out (DOUT), data clock (DCLK), a chip select ( $\overline{CS}$ ) and an Interrupt (INT). The serial input consists of 8-bit commands sent by the external controller to the Le78D11 VoSLAC device that can be followed with additional bytes of input data or can be followed by the Le78D11 VoSLAC device sending out bytes of data. All data input and output is MSB (D7) first and LSB (D0) last. All data bits are shifted in/out with respect to the DCLK while  $\overline{CS}$  is Low. The MPI will not accept a command or data byte of less than 8 bits; if more than 8 bits are

sent while  $\overline{\text{CS}}$  is Low, only the last 8 bits will be interpreted as the command or data byte when CS makes a transition to the High state. DCLK may be stopped in the High or Low state indefinitely without loss of information, but CS must only go high when DCLK is High. All data bytes are read or written one at a time, with  $\overline{\text{CS}}$  going High for at least the minimum off period before the next byte can be read or written.

The Le78D11 VoSLAC device is designed such that a single  $\overline{\text{CS}}$  can be used to interface several Le78D11 VoSLAC devices to the system controller. This is accomplished by daisy chaining several devices together. (Refer to the *Le77D11/Le78D11 Chip Set User's Guide*, document ID# 080716, for more information.)

The Le78D11 VoSLAC device can also be used with micro controllers that do not have separate DIN and DOUT pins, but only contain a single bidirectional serial data pin. This is accomplished by connecting the DOUT and DIN pins of the Le78D11 VoSLAC device together and tying them to the bidirectional DIO pin of the micro controller.

The Le78D11 VoSLAC device allows writing filter coefficient parameters to only one channel, thereby programming each channel separately. When writing filter coefficients or device parameters, only one channel should be enabled in the EC register, thereby programming each channel separately.

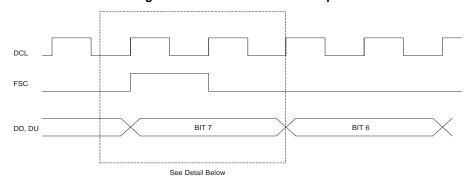

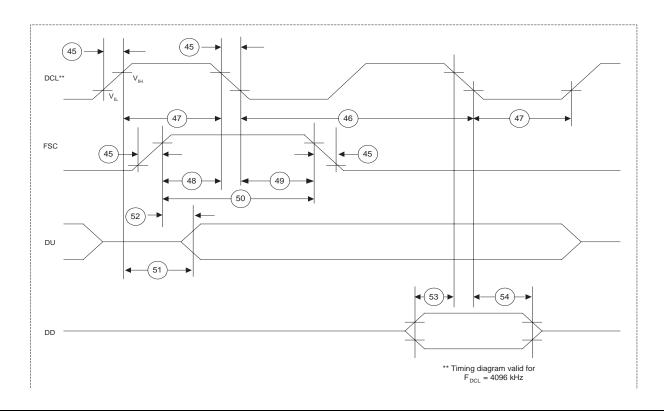

### **General Circuit Interface (GCI) Mode**

The Le78D11 VoSLAC device switches between PCM/MPI and GCI modes, depending on the pin assignment of FS/DCL and PCLK/FSC. The Le78D11 VoSLAC device powers-up assuming a PCM interface and therefore assumes PCLK is on the pin labeled PCLK/FSC and Frame Sync is on the pin labeled FS/DCL. While in PCM mode, if forty-eight or more cycles are detected on DCL between two rising edges of FSC, the Le78D11 VoSLAC device enters GCI mode. If at any time while the part is in GCI mode, a valid MPI command sequence appears on the DCLK/ S0 and  $\overline{\text{CS}}$  pins, the part immediately reverts to PCM/MPI mode. This is detected by counting eight low-to-high transitions of DCLK/S0 with  $\overline{\text{CS}}$  low.

#### **GCI Channel Assignment**

In the channel control block, the 8 kHz FSC pulse identifies the beginning of a frame, and all GCI downstream and upstream channels are referenced to it.

When the GCI mode pin (TSCA/G) is connected to DGND, the Le78D11 VoSLAC device selects standard GCI mode supporting two voice channels per GCI channel. Each device occupies a single GCI channel, and eight devices can be controlled over a single GCI bus. Logic inputs DCLK/S0, DIN/S1 and INT/S2 on the Le78D11 VoSLAC device determine the GCI channel assignment. These pins are normally hard-strapped to the selected channel. Downstream data coming in on the DD pin is extracted from the data stream and sent to the DSP core and control logic for sequential processing while data from the DSP and control circuits is sent out on the upstream DU pin.

When TSCA/G is connected to VCCD, the Le78D11 VoSLAC device selects a special mode of GCI operation where only one voice channel occupies each GCI channel, and the B2 voice channel is not used. When the single bearer channel mode is used, four Le78D11 VoSLAC devices handle the maximum of eight subscribers on the GCI bus. In this case, the S2 pin is ignored and the S1 and S0 pins identify the group of two GCI channels assigned to the Le78D11 VoSLAC device. This mode provides for support of 16 bit linear voice data over the GCI interface.

#### **GCI Bus Format and Command Structure**

The GCI bus provides communication for both control and voice data to the Le78D11 VoSLAC device. Each GCI bus consists of eight, four-byte GCI channels that contain voice and control information. Depending on the GCI mode, the Le78D11 VoSLAC device sends one or two complete GCI channels upstream on the DU pin and receives one or two channels from the downstream DD pin every 125 µs.

The four-byte GCI channels contain the following:

- One or Two voice bearer channels

- For standard GCI mode, B1 and B2 are reserved for voice channels 1 and 2.

- In single bearer channel mode, B2 is unused except when linear PCM mode is selected. In this case B1 and B2 data bytes are combined.

- One Monitor (M) channel for reading and writing control data and coefficients to the chip set.

- One Signaling and Control (SC) channel containing a 6-bit Command/Indicate (C/I) field for control information and a two

bit field with Monitor Receive and Monitor Transmit (MR and MX) bits for handshaking functions. All principal signaling (real

time critical) information is carried in the C/I field.

#### **PLL Clock Generator**

The PLL clock generator derives the Le78D11 VoSLAC device's internal DSP clock (49.152 MHz) and system clock (16.384 MHz) from a 512 kHz reference input This input can come from a number of sources depending on the device mode of operation.

In the GCI mode, the Le78D11 VoSLAC device automatically detects whether a 2.048 MHz or 4.096 MHz data clock (DCL) is being used and programs the Device Configuration Register 1 accordingly to provide the required reference.

In the PCM/MPI mode, the reference input clock can be derived from either PCLK or MCLK. The clock being supplied must be communicated to the Le78D11 VoSLAC device using the MPI by specifying its source and frequency in Device Configuration

Register 1. If the PCLK or MCLK frequency is not an exact multiple of 512 kHz, the difference must be communicated to the Le78D11 VoSLAC device by programming the Master Clock Correction Register.

If the PCLK frequency falls outside the range of 512 kHz to 8.192 MHz, then the MCLK pin must be selected as the reference input clock. In this case MCLK must still be synchronous to PCLK/FSC.

# **SLIC Device Interface (SLI)**

The SLIC Interface logic block controls the state of each Le77D11 device channel through the C3<sub>i</sub>, C2<sub>i</sub>, and C1<sub>i</sub> control pins. The SLIC state presented on these pins is decoded from the programmed VoSLAC device state. In the PCM/MPI mode, the VoSLAC device state is controlled by using the "Write VoSLAC Channel State" command, and by the downstream C/I field in GCI mode.

The SLIC device loop current limit is controlled by the voltage output on the VDC pin. The VDC output can be programmed to one of seven different levels using the "Write VoSLAC Channel State" command, providing a wide range of loop current settings.

Finally, the chopper clock output (CHCLK) can be programmed to either 85.3 or 256kHz operation, with a 10% high duty cycle. (applicable to the Le77D21 device only)

| C3 | C2 | C1 | Le77D11 Device<br>Operating Mode | Le77D21 Device<br>Operating Mode | Description                                                                                                                                                                                                 |

|----|----|----|----------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0  | 0  | Low Power Standby                | Low Power Standby                | Voice transmission disabled. Maximum loop current capability and loop current sensing range are reduced.                                                                                                    |

| 0  | 0  | 1  | Disconnect                       | Disconnect                       | SLIC channel is shut down and presents a high impedance to the line. Switching power supply is shut off.                                                                                                    |

| 0  | 1  | 0  | Normal Active                    | Normal Active                    | SLIC channel fully operational. A (TIP) is more positive than B(RING). Also used for on-hook transmission.                                                                                                  |

| 0  | 1  | 1  | Reverse Polarity                 | Reverse Polarity                 | Similar to normal active, but DC polarity is reversed so that the B(Ring) lead is more positive than the A (TIP) lead. Also used for on-hook transmission.                                                  |

| 1  | 0  | 0  | Ringing                          | Ringing                          | Ringing state with V <sub>AB</sub> set to K <sub>R</sub> • V <sub>IN</sub> . The switching supply maintains minimum headroom for the sourcing and sinking amplifiers in order to maximize power efficiency. |

| 1  | 0  | 1  | Line Test State                  | Line Test State                  | Similar to ringing state with reduced bias currents for lower noise. Loop current sensing range is limited. See IMT pin specifications.                                                                     |

| 1  | 1  | 0  | Reserved                         | Active + Test Load               | Normal Active with test switch enabled. (applicable to Le77D21 device only)                                                                                                                                 |

| 1  | 1  | 1  | Reserved                         | Ringing + Test Load              | Ringing with test switch enabled. (applicable to <b>Le77D21</b> device only)                                                                                                                                |

Table 1. Device Operating States

# **Line Supervision Processing**

The loop supervision functions include loop, ring trip, ground key and fault detection. To perform these functions, the Le78D11 VoSLAC device uses the following signals:

- Metallic current (IMT<sub>i</sub>\*)

- The Le77D11 device sets IMT<sub>i</sub> to 1/500th the loop current. It is converted to a voltage, V<sub>IMT</sub>, by either an internal or external (programmable) 4.7K resistor placed between the IMT<sub>i</sub> pin and VREF. The full scale for the IMT input is 204 μA, which corresponds to a metallic current of 102 mA.

- Logic level fault indication (F<sub>i</sub>)

- The Le77D11 device's fault detection outputs, F

<sub>1</sub> and F

<sub>2</sub>, are driven low when a longitudinal current fault or foreign voltage occurs.

- Tip (VA<sub>i</sub>), Ring (VB<sub>i</sub>) and Sense (VS<sub>i</sub>) voltages

- External 475K resistors placed between the voltages being sensed and the VA<sub>i</sub>, VB<sub>i</sub> and VS<sub>i</sub> Le78D11 VoSLAC device inputs allow voltages up to +/-100V to be measured. Then either internal or external (programmable) 4.7K resistors are placed between the VA<sub>i</sub>, VB<sub>i</sub> and VS<sub>i</sub> Le78D11 VoSLAC device inputs and VREF to form voltage dividers.

#### Note:

<sup>\* &</sup>quot;i" denotes channel number.

#### **Loop Detection**

Loop detection is enabled for all Le78D11 device channel states except Disconnect and Ringing. The Le78D11 VoSLAC device detects an off-hook condition using the Hook Switch current threshold (ITH) variable. Every 500 µs the IMT value coming from the Le77D11 device is compared to ITH. When the result has stayed constant for the duration of the programmed debounce interval, the Hook bit will be set accordingly. The threshold levels and debounce periods are independently programmable.

#### **Ring Trip Detection**

Ring trip detection is mutually exclusive to Loop detection. In the ringing state, the Le78D11 VoSLAC device computes the mean square current in the ringing current IMT waveform over one cycle of ringing. The result of this computation is compared to RTSL, a programmable ring trip threshold. The integration period is programmable in 4 ms increments through the ring trip period parameter, RTSLP, which should be chosen to be close to the period of the ringing voltage (i.e. 12 for 20 Hz ringing and 10 for 25 Hz, default is 11 = 44ms).

Using ARR set to Zero, after the Le78D11 VoSLAC device transitions from ringing to ringtrip, the device should next be programmed to enter a non-ringing state.

#### Thermal Overload

When the die temperature around the two-wire interface of a Le77D11 device channel reaches approximately 165° C, the Le77D11 device pulls the corresponding IMT<sub>i</sub> pin above the IMT TEMPA threshold voltage. The Le78D11 VoSLAC device sets the TEMPA bit in the Signaling Register.

#### **DC Fault Detection**

Foreign DC voltages can be detected using the VFTD threshold. VFTD is compared against the output of a low pass 5 Hz filter whose input is VA+VB. Whenever the output is greater than VFTD, the DCFAULT bit in the signaling register is set.

B-to-ground faults that produce currents within the range of normal ground key currents cannot be recognized as a fault. However, this type of fault can be recognized as a ground key that persists for an excessively long time.

#### AC Fault Detection

Low level power crosses can occur that fail to activate any of the external protection devices. In this situation, the chip set must differentiate between unacceptable power cross voltage levels and low level longitudinal levels that do not affect the operation of the Voice over Broadband SLIC/VoSLAC device line card. This is controlled by the AC fault threshold VFTA. VFTA is compared against  $|X_i|$ , where  $X_i$  is the AC portion of  $VA_i + VB_i$ , which is rectified and averaged over a 44 ms period. Whenever the sum is greater than VFTA, the ACFAULT bit in the signaling register is set.

#### Loss of Power

When either of the VS<sub>i</sub> voltages sensed by the Le78D11 VoSLAC device drops below a programmable threshold, TVS, the Le78D11 VoSLAC device signals this condition by setting the appropriate VS<sub>i</sub> bits in the Global Device Status register. The polarity of the voltage is inverted: negative VS voltages will read back as positive values. When setting the sense threshold using the "Write Loop Supervision Parameter" command, a positive value should be used when monitoring negative voltages.

#### Clock Failure Alarm (CFAIL)

The internal 16.384 MHz system clock produced by the PLL is validated by comparing it with the frame sync signal which is assumed to be always toggling at an 8 kHz rate. The number of 16.384 MHz system clocks that occur between the rising edges of the frame sync signal are constantly monitored and if the number of system clocks exceed 2052 or fall below 2044, the Le78D11 VoSLAC device indicates this condition by setting the CFAIL bit located in the Global Device Status Register. During the time CFAIL is set, the Le78D11 VoSLAC device digital signal processor is halted, preventing processing errors due to an inaccurate system clock.

#### **Voice Signal Processing**

The principle function of the Le78D11 VoSLAC device is to handle the analog-to-digital and digital-to-analog conversions, along with the compression and expansion functions in order to interface the analog voice signal to the digital backplane. The Le78D11 VoSLAC device may be programmed to perform A-law or  $\mu$ -law companding, ADPCM compression, or 16-bit linear two's complement conversion.

In addition, the Le78D11 VoSLAC device has a number of digital filters that provide gain adjustments, distortion correction and equalization, 2-wire impedance matching, and 4-wire echo cancellation. Coefficient generation software (WinSLAC™) is available for optimizing the programmable filters in order to satisfy the system transmission requirements of multiple markets. From the Le78D11 VoSLAC device's point of view, the signal path from the digital-to-analog side is the receive path, while the analog-to-digital direction is the transmit path.

#### **Codec Function**

The companding type (A-law/µ-law/ADPCM) is software programmable and may be disabled to send the 16-bit linear two's complement sequence directly to the backplane. When ADPCM at 32 kbps or 24 kbps (as defined in ITU recommendation G.726.

ADPCM) is selected, data is output in the normal 8-bit PCM time slot. The data is output in the most significant bits of the time slot, and the unused bits (the 4 LSBs for 32 kbps, the 5 LSBs for 24 kbps) are filled with zeroes.

#### **Two-Wire Impedance Matching**

Two programmable digital feedback paths are provided in the Le78D11 VoSLAC device that allow some components of the transmit signal  $(V_{IN})$  back into the receive path  $(V_{OUT})$  in order to modify the effective two-wire input impedance of the Le77D11 device. The objective is to program each of these feedback paths to create an impedance match at tip and ring in order to minimize two-wire echo.

#### **Frequency Response Correction and Equalization**

The Le78D11 VoSLAC device contains digital, programmable filters in both the receive and transmit directions that can be programmed for line equalization or correction of any attenuation distortion introduced by input impedance matching.

#### **4-Wire Echo Cancellation**

A digital, programmable balance filter is used to cancel 4-wire echo by summing a filtered version of the receive signal into the transmit path. The purpose of the this filter is to replicate an inverted echo signal so that the actual echo will be eliminated from the transmit path. In the Le78D11 VoSLAC device, this filter has a single tap IIR component and 13 taps for the FIR portion, with a sampling rate of 16 kHz. The Le78D11 VoSLAC device may be programmed with static filter coefficients based on expected line conditions. It may also be placed in adaptive balance mode, in which case the DSP uses an adaptive algorithm to modify the filter coefficients in order to minimize the 4-wire echo. The Le78D11 VoSLAC device decides when to update the filter coefficients and when to stop adaptation based on user programmable control parameters.

#### **Gain Adjustments**

The Le78D11 VoSLAC device has programmable gain blocks in both receive and transmit paths.

The transmit path has two programmable gain blocks. The AX gain block is immediately before the A/D converter (ADC) and gives a gain of 0 dB or +6.02 dB. The digital GX block is designed to provide a gain from 0 to +12dB with better than 0.1db step size. Other gains up to a maximum of 15.6dB may be programmed, including the ability to cut-off the transmit signal.

The receive path has two programmable loss blocks. The AR analog gain occurs immediately after the D/A converter (DAC) and may be programmed to be 0 dB or –6 dB. The digital GR block is designed to provide from 0 to –12dB of loss with better than 0.1dB step size. Additional loss may be programmed, including the ability to cut-off the receive path.

### **Tone Detection and Signal Generation**

#### **Dual Tone Multi-Frequency (DTMF) Detection**

DTMF allows signaling using voice frequency signals. This function is typically used for telephone keypad tone dialing. The Le78D11 VoSLAC device decodes the dual tone signals into a 4-bit number and puts it into the signaling register with indication that a new digit has been detected.

#### Modem/Fax Tone Detection

When the relative power in the frequency band of  $2100 \pm 20$  Hz or  $1100 \pm 38$  Hz is greater than 6 dB with respect to the power outside the band, then a modem/fax tone is detected. There are modem/fax tone detectors in both the receive and transmit paths of the Le78D11 VoSLAC device. If either tone detector determines that a modem/fax tone is present, the TONE bit transitions from 0 to 1 and an interrupt may be generated. The DTMF3:DTMF0 bits in the signaling register indicate which tone was detected (0011 = 1100 Hz, 0001 = 2100 Hz). Once a modem/fax tone is detected, the TONE bit remains high until the HOOK bit transitions from 1 to 0. The detection of an on hook transition automatically resets the TONE bit to 0.

#### **Signal Generation**

The Le78D11 VoSLAC device has three tone generators available per channel for general call progress tone generation and test signal generation. In addition, the following special purpose tone generation functions are available.

#### **Ringing Generation**

The Voice Access chip set can generate and output a ringing signal without the need for an external ringing generator and ring relay. Both trapezoidal and sine wave ringing signals can be generated from the Le78D11 signal generator A. The ringing frequency, amplitude, DC offset, and crest factor for trapezoidal waveforms are programmable. Internal ringing is always initiated synchronous to the line voltage  $V_{AB}$ , and may be terminated after a ring trip detection, either immediately (ZXR = 1), or at the zero crossing (ZXR = 0).

#### **DTMF Generation**

DTMF generation can be accomplished easily with command 66h/67h Write/Read Signal Generator B Control. This command automatically programs Signal Generator B with one of the 16 standard DTMF tones.

#### **FSK Generation**

The Le78D11 VoSLAC device has the ability to generate phase continuous FSK tones at a 1200 baud rate. These tones can be used for a variety of purposes such as Calling Number Delivery (CND), better known as Caller ID, and Visual Message Waiting

Indication (VMWI). It allows the called Customer Premises Equipment (CPE) to receive a calling party's name and directory number along with the date and time of the call.

There are a number of protocols defined, which the chip set can support. In one case the information is sent between the first and second ring bursts, starting as early as 500 ms after the first ring, and ending at least 200 ms before the second ring burst. The information is sent using analog, phase coherent FSK at a 1200 bps rate. The Le78D11 VoSLAC device is designed to provide this feature and can be programmed to initiate or terminate the Caller ID stream as required.

#### **Teletax Generation**

Teletax signals send call charge information to the subscriber equipment. These signals are normally sent during the Active Normal mode. The Le78D11 VoSLAC device supports teletax through metering tone bursts which are summed into the receive path DAC and output on VOUT. The 12 or 16 kHz metering burst ramps up over 20ms to the metering target level, MVO, when the teletax state is selected, and ramps back down when the active state is selected. MVO is specified as the peak value of the metering voltage (0 to 1020 mV) at the VOUT pin. If the ABRUPT bit is set, the 12 or 16 kHz signal ramps up or down almost immediately (< 5 ms).

#### **Line Measurement**

There is one line measurement block per Le78D11 VoSLAC device, which allows measurement of various line and circuit parameters such as leakage resistance, line capacitance, ringer capacitance, receiver off hook, foreign voltage, idle channel noise, echo gain, etc. Most tests are performed in combination with appropriate signal generation. When a line measurement is initiated, the adaptive feature of the echo cancellation filter is frozen for both channels. The line measurement block automatically connects to the enabled channel.

The Le78D11 VoSLAC device returns incorrect Rloop values in Polarity Reversal states. To measure loop resistance in the Polarity Reversal state, the user must read Vab and Vimt, then compute the resistance. Disable Filter 1 and Filter 2 before taking the line measurements on Vimt or Vab inputs (CLM1=001 or CLM1=0110).

### **Band Gap Voltage Reference**

All analog reference voltages are derived from a band gap reference with a very low temperature coefficient. Bias currents are derived from the IREF pin current.

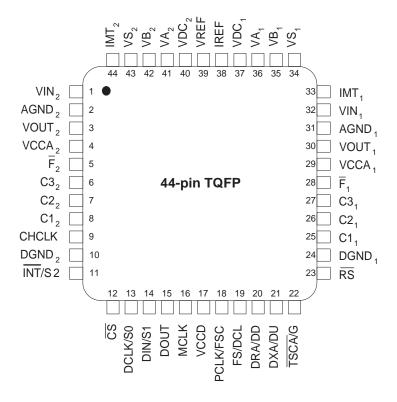

#### CONNECTION DIAGRAM

#### Note:

Pin 1 is marked for orientation.

# **PIN DESCRIPTIONS**

| Pin Name                              | Туре                               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|---------------------------------------|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                       |                                    | Power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| AGND <sub>1</sub> , AGND <sub>2</sub> |                                    | Analog section ground return for each channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| DGND <sub>1</sub> , DGND <sub>2</sub> |                                    | Digital section ground returns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| VCCA <sub>1</sub> , VCCA <sub>2</sub> |                                    | +3.3 VDC supplies to the analog section in each channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| VCCD                                  |                                    | +3.3 VDC supply to all digital sections                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                       | PCM Interface                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| DRA/DD                                | Input*                             | PCM mode, the receive PCM data is input serially through the DRA pin. The data input is received every 125 μs and is shifted in, MSB first, in 8-bit PCM or 16-bit linear bursts at the PCLK rate. For the GCI mode, downstream receive and control data is accepted on this pin.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| DXA/DU                                | Output*                            | For the PCM highway, the transmit PCM data is transmitted serially through the DXA pin. The transmission data output is available every 125 µs and is shifted out, MSB first, in 8-bit PCM or 16-bit linear bursts at the PCLK rate. DXA is high impedance between bursts and while the device is in the inactive mode. For the GCI mode, upstream transmit and signaling data is transferred on this pin.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| FS/DCL                                | Input*                             | For PCM operation, this pin functions as the Frame Sync input. PCM operation is selected by the presence of an 8 kHz Frame Sync signal on this pin in conjunction with the PCLK (see below). This 8 kHz pulse identifies the beginning of a frame. The Le78D11 VoSLAC device references individual time slots with respect to this input, which must be synchronized to PCLK. In GCI mode, the rate at which data is shifted into or out of the pin is a derivative of this DCL clock.                                                                                                                                                                                                     |  |  |  |  |  |

| MCLK                                  | Input*                             | For PCM backplane operation, a DSP master clock is connected to this pin. A signal is required only for PCM backplane operation when PCLK is not used as the master clock. MCLK can be a wide variety of frequencies. Upon initialization the MCLK input is disabled, and relevant circuitry is driven by PCLK. The MCLK connection is established under user control. This pin is not used in GCI mode, and should be tied to ground.                                                                                                                                                                                                                                                     |  |  |  |  |  |

| PCLK/FSC                              | Input*                             | For PCM operation, this pin is the PCM Clock input. PCM operation is selected by the presence of a PCLK signal on this pin in conjunction with the FS on the FS pin (see below). This clock determines the rate at which PCM data is serially shifted into and out of the PCM ports. PCLK must be an integer multiple of the FS frequency. The minimum clock frequency for linear/companded data plus signaling data is 256 kHz. For GCI operation, this pin functions as Frame Sync. The FSC signal is an 8 kHz pulse that identifies the beginning of a frame. The Le78D11 VoSLAC device references individual time slots with respect to this input, which must be synchronized to DCL. |  |  |  |  |  |

| TSCA/G                                | Output<br>(PCM)<br>Input<br>(GCI)* | For PCM backplane operation, $\overline{\text{TSCA}}$ is active low when PCM data is output on the DXA pin. The outputs are open-drain and are normally inactive (high impedance). Pull-up loads should be connected to VCCD. When GCI mode is selected, one of two GCI modes may be selected by connecting $\overline{\text{TSCA}}/\text{G}$ to DGND or VCCD.                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| MPI Interface                         |                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| CS                                    | Input*                             | For PCM backplane operation, a logic low placed on this pin enables serial data transmission into, or out of, the DIN/DOUT pin. Not used in GCI mode (pin should be pulled high in GCI mode).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| DCLK/S0                               | Input*                             | Data clock for the MPI control interface. For GCI operation, this pin is device address bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| DIN/S1                                | Input*                             | For PCM backplane operation, control data is serially written into the Le78D11 VoSLAC device via the DIN pin with the MSB first. The data clock (DCLK) determines the data rate. This pin may also be tied to DOUT, on systems using a single bi-directional data line (Bit 7 in register DCR2 must be low when DIN is tied to DOUT). For GCI operation, this pin is device address bit 1.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| DOUT                                  | Output*                            | For PCM backplane operation, control data is serially read out of the Le78D11 VoSLAC device via the DOUT pin with the MSB first. The data clock (DCLK) determines the data rate. This pin may also be tied to DIN, on systems using a single bi-directional data line (Bit 7 in register DCR2 must be low when DIN is tied to DOUT). This pin is not used in GCI mode, and must remain unconnected.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| ĪNT/S2                                | Output<br>(PCM)<br>Input<br>(GCI)* | For PCM operation, when a subscriber line requires service, this pin goes to a logic 0 to interrupt a higher level processor. Several registers work together to control operation of the interrupt: Signaling and Global Interrupt Registers with their associated Mask Registers, and the Interrupt Register. See the description at configuration register 6 (Mask) for operation. Logic drive is selectable between open drain and TTL-compatible outputs. In GCI mode, this pin functions as device address bit 2.                                                                                                                                                                    |  |  |  |  |  |

| RS                                    | Input*                             | Active low reset for the Le78D11 VoSLAC device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Pin Name                                                                                                   | Туре         | Description                                                                                                                                                                                                                                                                 |

|------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Line State Contro                                                                                          | ol           |                                                                                                                                                                                                                                                                             |

| C1 <sub>1</sub> , C2 <sub>1</sub> , C3 <sub>1</sub><br>C1 <sub>2</sub> , C2 <sub>2</sub> , C3 <sub>2</sub> | Output       | Per channel outputs which control the Le77D11 device line states.                                                                                                                                                                                                           |

| VDC <sub>1</sub> , VDC <sub>2</sub>                                                                        | Output       | Sets a programmable current limit threshold for the DC feed in the Le77D11 device. Connects to the corresponding RDC1 and RDC2 pins of the Le77D11 device through the R <sub>DCi</sub> resistors.                                                                           |

| $\overline{F}_1, \overline{F}_2$                                                                           | Input*       | Fault detect pin for channels 1 and 2. A low indicates a fault for the respective channel, which can be triggered by large longitudinal voltages or ground key.                                                                                                             |

| CHCLK                                                                                                      | Output       | Software programmable 256 or 85.3 kHz clock for the switching regulator in the Le77D11 device (applicable to the Le77D11 device only).                                                                                                                                      |

| Line Supervision                                                                                           | Processing I | nputs                                                                                                                                                                                                                                                                       |

| IMT <sub>1</sub> , IMT <sub>2</sub>                                                                        | Input        | Connects to the IMTi leads of the Le77D11 device. I <sub>IMT</sub> = I <sub>LOOP</sub> • K <sub>DC</sub>                                                                                                                                                                    |

| VA <sub>1</sub> , VA <sub>2</sub> ,<br>VB <sub>1</sub> , VB <sub>2</sub>                                   | Input        | Connects to the A and B leads of the Le77D11 through a 475 k $\!\Omega$ resistor.                                                                                                                                                                                           |

| VS <sub>1</sub> , VS <sub>2</sub>                                                                          | Input        | General purpose voltage sense inputs of the Le77D11 devices can connect to high voltage supplies through a 475 k $\Omega$ resistor.                                                                                                                                         |

| Voice Data                                                                                                 | •            |                                                                                                                                                                                                                                                                             |

| VIN <sub>1</sub> , VIN <sub>2</sub>                                                                        | Input        | These pins are the inputs for the analog transmit signals (VOUTi) from the Le77D11 device. The Le78D11 VoSLAC device converts these signals to digital words and processes them. After processing, they are multiplexed into serial time slots and sent out of the DXA pin. |

| VOUT <sub>1</sub> , VOUT <sub>2</sub>                                                                      | Output       | The Le78D11 VoSLAC device extracts and processes voice data from time slots on DRA serial data port. After processing, the Le78D11 VoSLAC device converts the voice data to analog signals and outputs it at these pins to the Le77D11 device.                              |

| Band Gap Voltag                                                                                            | e Reference  |                                                                                                                                                                                                                                                                             |

| IREF                                                                                                       | Input        | A 69.8 k external resistor (R <sub>REF</sub> ) connected between this pin and analog ground generates an accurate, on-chip reference current for the A/D's and D/A's on the Le78D11 chip.                                                                                   |

| VREF                                                                                                       | Output       | This pin provides a 1.4 V, single ended reference to the Le77D11 device to which the Le78D11 VoSLAC device is connected.                                                                                                                                                    |

### Note:

<sup>\* 5</sup> V tolerant pin.

### **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed under *Absolute Maximum Ratings* can cause permanent device failure. Functionality at or above these limits is not implied. Exposure to Absolute Maximum Ratings for extended periods can affect device reliability.

| Storage Temperature                               | -60°C < T <sub>A</sub> < +125°C                                 |

|---------------------------------------------------|-----------------------------------------------------------------|

| Ambient Temperature, under Bias                   | -40°C ≤ T <sub>A</sub> ≤ +85°C                                  |

| Ambient relative humidity (non condensing)        | 5 to 95%                                                        |

| V <sub>CCA</sub> with respect to DGND             | -0.4 to + 4.0 V                                                 |

| V <sub>CCA</sub> with respect to V <sub>CCD</sub> | -0.4 to + 0.4 V                                                 |

| V <sub>CCD</sub> with respect to DGND             | -0.4 to + 4.0 V                                                 |

| AGND with respect to DGND                         | ±50 mV                                                          |

| 5 V tolerant digital pins with respect to DGND    | -0.4 to 5.5V or V <sub>CCD</sub> + 2.37 V, whichever is smaller |

| Any other pin with respect to DGND                | -0.4 to V <sub>CCD</sub> +0.4 V                                 |

| Latch up immunity (any pin)                       | ±100 mA                                                         |

#### Package Assembly

The standard (non-green) package devices are assembled with industry-standard mold compounds, and the leads possess a tin/ lead (Sn/Pb) plating. These packages are compatible with conventional SnPb eutectic solder board assembly processes. The peak soldering temperature should not exceed 225°C during printed circuit board assembly.

The green package devices are assembled with enhanced environmental compatible lead (Pb), halogen, and antimony-free materials. The leads possess a matte-tin plating which is compatible with conventional board assembly processes or newer lead-free board assembly processes. The peak soldering temperature should not exceed 245°C during printed circuit board assembly. Refer to IPC/JEDEC J-Std-020B Table 5-2 for the recommended solder reflow temperature profile.

### **OPERATING RANGES**

Legerity guarantees the performance of this device over commercial (0° to 70°C) and industrial (-40° to 85°C) temperature ranges by conducting electrical characterization over each range, and by conducting a production test with single insertion coupled to periodic sampling. These characterization and test procedures comply with section 4.6.2 of Bellcore TR-TSY-000357 Component Reliability Assurance Requirements for Telecommunications Equipment.

# **Environmental Ranges**

| Ambient Temperature       | -40°C ≤ T <sub>A</sub> ≤ +85°C |

|---------------------------|--------------------------------|

| Ambient Relative Humidity | 15 to 85%                      |

# **Electrical Maximum Ranges**

| Analog Supply V <sub>CCA</sub>  | +3.3 V ± 5%<br>V <sub>CCD</sub> ± 50mV |

|---------------------------------|----------------------------------------|

| Digital Supply V <sub>CCD</sub> | +3.3 V ± 5%                            |

| DGND                            | 0 V                                    |

| AGND                            | ±10 mV                                 |

| 5V Tolerant Digital Pins        | DGND to +5.25V                         |

#### **ELECTRICAL CHARACTERISTICS**

### **Power Dissipation**

| Description                             | Test Conditions                         | Min | Тур | Max | Unit |

|-----------------------------------------|-----------------------------------------|-----|-----|-----|------|

| La 70D44 VaOLAO desdes Bassas           | Two channels Standby                    |     | 100 | 120 |      |

| Le78D11 VoSLAC device Power Dissipation | One channel Active, one channel Standby |     | 140 | 160 | mW   |

| 2.00.pa                                 | Two channels Active                     |     | 180 | 210 |      |

# **SPECIFICATIONS**

# **System Specifications**

The performance targets defined in this section are for a system using the VE770 series chip set. Specifications for the Le77D11 device are published separately.

| No    | ltem                                     | Condition                                                                      | Min | Тур | Max | Unit | Note      |

|-------|------------------------------------------|--------------------------------------------------------------------------------|-----|-----|-----|------|-----------|

| 1     | Peak Ringing Voltage                     | Ringing mode,<br>R <sub>L</sub> = 1500 $\Omega$ ,                              |     | 70  | 90  | V    |           |

| 2     | Output Impedance during internal ringing | Ringing mode, Le78D11 VoSLAC device generating internal ringing                |     | 200 |     | Ω    |           |

| 3     | Sinusoidal Ringing THD                   | Ringing mode,<br>$R_L = 1500 \Omega$ generating internal<br>sinusoidal ringing |     | 2   |     | %    |           |

| Signa | Signaling Performance Limits             |                                                                                |     |     |     |      |           |

| 1     | Hook switch threshold                    | ITH = 10 mA                                                                    | 7   |     | 13  | mA   |           |

| 2     | Hook switch hysteresis                   | All ITH settings                                                               |     | 10  |     | %    | <u>2.</u> |

| 3     | Internal Ring Trip Accuracy              | RTSL = 2.2 W                                                                   | -20 |     | +20 | %    |           |

# **Device DC Specifications**

Typical values are for TA = 25°C and nominal supply voltages. Minimum and maximum values are over the temperature and supply voltage ranges given in *Operating Ranges* except where noted.

| No. | ltem                                                                             | Condition                                   | Min                      | Тур            | Max   | Unit | Note      |

|-----|----------------------------------------------------------------------------------|---------------------------------------------|--------------------------|----------------|-------|------|-----------|

| 1   | Digital Input Low Voltage                                                        |                                             |                          |                | 0.80  | V    | <u>1.</u> |

| 2   | Digital Input High Voltage                                                       |                                             | 2.0                      |                |       | V    | <u>1.</u> |

| 3   | Digital Input Leakage Current                                                    | 0 < V < V <sub>CCD</sub>                    | -15                      |                | +15   |      |           |

|     | (except MCLK)                                                                    | Otherwise                                   | -120                     |                | +180  | μA   |           |

| 4   | MCLK Digital Input Leakage<br>Current                                            | 0 to 5.35 V                                 | -120                     |                | +180  | ·    |           |

| 5   | Digital Input hysteresis ( $\overline{F}_{i,}$ PCLK, FS, MCLK, DIN, DRA)         |                                             | 0.15                     | 0.225          | 0.3   |      | 1.        |

| 6   | Digital Output Low Voltage (all digital pins)                                    | I <sub>OL</sub> = 1 mA                      |                          |                | 0.4   |      |           |

| 7   | Digital Output Low Voltage (INT, TSCA)                                           | I <sub>OL</sub> = 14 mA                     |                          |                | 0.4   | V    |           |

| 8   | Digital Output High Voltage (All outputs except INT in open drain mode and TSCA) | Ι <sub>ΟΗ</sub> = 400 μΑ                    | V <sub>CCD</sub><br>-0.4 |                |       |      |           |

| 9   | Digital Output source impedance                                                  | Drive low                                   |                          | 400            |       | 0    |           |

| 3   | Digital Output source impedance                                                  | Drive high                                  |                          | 1000           |       | Ω    |           |

| 10  | Digital Output leakage current,                                                  | 0 < V < V <sub>CCD</sub>                    | -15                      |                | +15   | μA   |           |

| 10  | high impedance state                                                             | Otherwise                                   | -120                     |                | +180  | μΛ   |           |

| 11  | VIN <sub>i</sub> Input voltage range (Relative                                   | AX = 0 dB                                   |                          | ±1.02          |       | Vpk  | <u>4.</u> |

|     | to V <sub>REF</sub> )                                                            | AX = 6.02 dB                                |                          | ±0.51          |       | VPK  | 1         |

| 12  | Offset voltage allowed on VIN <sub>i</sub>                                       |                                             | -50                      |                | +50   | mV   |           |

| 13  | VIN <sub>i</sub> Input Impedance                                                 |                                             |                          | 1.0            |       | MΩ   |           |

| 14  | VIN <sub>i</sub> Leakage Current                                                 |                                             | -10                      |                | 10    | μA   |           |

| 15  | VREF Output voltage                                                              | Load current = 0 to 10 mA<br>Source or Sink | 1.344                    | 1.4            | 1.456 | V    |           |

| 16  | Output drive current for VREF                                                    |                                             | 10                       | 25             |       | mA   |           |

| 17  | Capacitance load on VREF or VOUT <sub>i</sub>                                    |                                             | 0                        |                | 200   | pF   | <u>1.</u> |

| 18  | VOUT <sub>i</sub> Output Voltage range<br>(Relative to V <sub>REF</sub> )        | AR = 0 dB $AR = -6.02 dB$                   |                          | ±1.02<br>±0.51 |       | Vpk  | <u>4.</u> |

|     |                                                                                  |                                             |                          |                |       |      |           |

| No. | Item                                                                                                    | Condition                               | Min | Тур       | Max | Unit | Note      |

|-----|---------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|-----------|-----|------|-----------|

| 19  | VOUT <sub>i</sub> offset Voltage                                                                        | DISN off                                | -40 |           | +40 | m\/  | 4.        |

| 19  | VOOT TOUSET VOILAGE                                                                                     | DISN on                                 | -80 |           |     | 4.   |           |

| 20  | VOUT <sub>i</sub> Output leakage current                                                                | 0 < V <sub>OUT</sub> < V <sub>CCA</sub> | -10 |           |     | μΑ   |           |

| 21  | Input Impedance for VA <sub>i</sub> , VB <sub>i</sub> , and                                             | Internal resistor mode                  |     | 3490      |     | Ω    |           |

| 21  | VS <sub>i</sub> pins                                                                                    | External resistor mode                  |     | 1         |     | MΩ   |           |

| 22  | Input impedance for IMT <sub>i</sub> pins                                                               |                                         | Ω   | <u>1.</u> |     |      |           |

| 22  | input impedance for intripuis                                                                           | External resistor mode                  |     | 1         |     | ΜΩ   | <u>1.</u> |

| 23  | Maximum input current for $VA_i$ , $VB_i$ , $VS_i$ and $IMT_i$ pins                                     | Internal resistor mode                  |     |           | 950 |      |           |

| 24  | Input leakage current for VA <sub>i</sub> , VB <sub>i</sub> , VS <sub>i</sub> and IMT <sub>i</sub> pins | External resistor mode                  | -1  |           | +1  | μΑ   |           |

| 25  | IMT TEMPA threshold voltage                                                                             |                                         | 2.4 | 2.65      | 3.0 | V    |           |

| 26  | IMT TEMPA duration                                                                                      |                                         | 125 |           |     | μs   | <u>2.</u> |

| 27  | VDC voltage accuracy                                                                                    | 0.2 to 1.4 V                            | -70 |           | +70 | mV   |           |

# **Transmission Specifications**

Table 2. 0 dBm0 Voltage Definitions with Unity Gain in X, R, GX, GR, AX, and AR

| Signal at Digital Interface             | Transmit | Receive | Unit |

|-----------------------------------------|----------|---------|------|

| A-law digital mW or equivalent (0 dBm0) | 0.5026   | 0.5026  |      |

| μ-law digital mW or equivalent (0 dBm0) | 0.4987   | 0.4987  | Vrms |

| ±5,800 peak linear coded sine wave      | 0.5026   | 0.5025  |      |

| No. | Item                                                     | Condition                                                                            | Min   | Тур        | Max   | Unit   | Note      |

|-----|----------------------------------------------------------|--------------------------------------------------------------------------------------|-------|------------|-------|--------|-----------|

| 1   | Gain accuracy, D-A or A-D                                | 0 dBm0, 1014 Hz<br>AR = AX = GR = GX = 0 dB,<br>DISN, R, X, B and Z filters disabled | -0.25 | 0          | +0.25 |        |           |

|     | A-D + D-A                                                | Temperature = 70°C                                                                   | -0.15 | 0          | +0.15 |        | <u>3.</u> |

|     | A-D + D-A                                                | Variation over temperature                                                           | -0.1  | 0          | +0.10 |        |           |

| 2   | Level set error (Error between setting and actual value) | A-D AX + GX<br>D-A AR + GR                                                           | -0.1  | 0          | 0.1   |        |           |

| 3   | GX step size                                             | 0 ≤ GX < 12 dB                                                                       |       | 0.1        |       |        | <u>1.</u> |

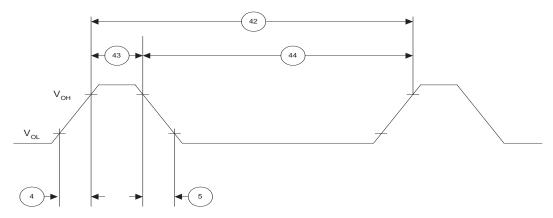

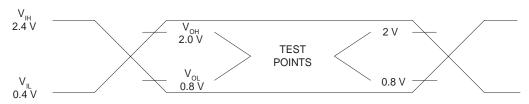

| 4   | GR step size                                             | -12 ≤ GR ≤ 0 dB                                                                      |       |            | 0.1   | dB     | <u>1.</u> |