# **STLC5046**

# Programmable four channel CODEC and filter

# **Features**

- Programmable monolithic 4 channel

- CODEC/Filter

- Single +3.3 V supply

- Pin-strap / MCU control mode

- A/µ Law programmable

- Linear coding (16 bits) option

- PCM highway format automatically detected: 1.536 or 1.544 MHz; 2.048, 4.096, 8192 MHz

- TX gain programming: 16 dB range; <0.1 dB step

- RX gain programming: 26 dB range; <0.1 dB step

- Programmable time slot assignment

- Digital and analog loopbacks

- SLIC control port

- Static mode (16 I/Os)

- Dynamic mode (12 I/Os + 4 CS)

- LQFP64 package

- PCM in HI-Z mode

# Description

The STLC5046 is a monolithic programmable 4 channel codec and filter. It operates with a single +3.3 V supply.

The analog interface is based on a receive output buffer driving the SLIC RX input and on an amplifier input stage.

Due to the single supply voltage a proper mid supply reference level is generated internally by the device and all analog signals are referred to this level (AGND).

The PCM interface uses one common 8 kHz frame sync, pulse for transmit and receive direction. The bit clock can be selected between four standards: 1.536/1.544 MHz, 2.048 MHz, 4.096 MHz, 8192 MHz. Device programmability is achieved by means of 41 registers allowing to set the different parameters like TX/RX gains, encoding Law (A/µ), time slot assignment, independent channels power up/down, loopbacks, PCM bits offset.

Thanks to pin-strap option, the most significant of the above parameters can be set by hardware connection of dedicated pins. This allow to use this device also on line card without MCU on board. When pin-strap option is selected different pins of the device will change their function (see pin description).

In MCU control mode the STLC5046 can be programmed via serial interface running up to 4 MHz.

One interrupt output pin is also provided.

#### Table 1. **Device summarv**

| Order code                | Temperature range | Package | Packing |

|---------------------------|-------------------|---------|---------|

| E-STLC5046 <sup>(1)</sup> | -40°C to +85°C    | LQFP64  | Tube    |

1. ECOPACK<sup>®</sup> (see Section 7)

# Contents

| 1 | Block | ck diagram and pin connection |                                        |  |

|---|-------|-------------------------------|----------------------------------------|--|

|   | 1.1   | Pin desc                      | cription                               |  |

| 2 | Funct | ional de                      | escription                             |  |

|   | 2.1   | Power o                       | n initialization                       |  |

|   | 2.2   | Power d                       | own state                              |  |

|   | 2.3   | Transmit                      | t path                                 |  |

|   | 2.4   | Receive                       | path                                   |  |

|   | 2.5   |                               | ·<br>erface                            |  |

|   |       | 2.5.1                         | MCU mode                               |  |

|   |       | 2.5.2                         | Pin-strap mode                         |  |

|   | 2.6   | Control                       | interface                              |  |

|   | 2.7   | SLIC co                       | ntrol interface                        |  |

|   |       |                               |                                        |  |

| 3 | Regis | ters ado                      | dresses                                |  |

|   | 3.1   | Register                      | rs description                         |  |

|   |       | 3.1.1                         | Configuration register (CONF) 19       |  |

|   |       | 3.1.2                         | I/O Direction register (DIR)19         |  |

|   |       | 3.1.3                         | I/O Data register channel #0 (DATA0)20 |  |

|   |       | 3.1.4                         | I/O Data register channel #1 (DATA1)20 |  |

|   |       | 3.1.5                         | I/O Data register channel #2 (DATA2)21 |  |

|   |       | 3.1.6                         | I/O Data register channel #3 (DATA3)22 |  |

|   |       | 3.1.7                         | Transmit Gain channel #0 (GTX0)23      |  |

|   |       | 3.1.8                         | Transmit Gain channel #1 (GTX1)23      |  |

|   |       | 3.1.9                         | Transmit Gain channel #2 (GTX2)24      |  |

|   |       | 3.1.10                        | Transmit Gain channel #3 (GTX3)24      |  |

|   |       | 3.1.11                        | Receive Gain channel #0 (GRX0)25       |  |

|   |       | 3.1.12                        | Receive Gain channel #1 (GRX1)25       |  |

|   |       | 3.1.13                        | Receive Gain channel #2 (GRX2)         |  |

|   |       | 3.1.14                        | Receive Gain channel #3 (GRX3)         |  |

|   |       | 3.1.15                        | Transmit Time Slot channel #0 (DXA0)27 |  |

|   |       | 3.1.16                        | Transmit Time Slot channel#1 (DXA1)    |  |

|   |       | 3.1.17                        | Transmit Time Slot channel #2 (DXA2)   |  |

|   | 3.1.18         | Transmit Time Slot channel #3 (DXA3)         |

|---|----------------|----------------------------------------------|

|   | 3.1.19         | Receive Time Slot channel #0 (DRA0)          |

|   | 3.1.20         | Receive Time Slot channel #1 (DRA1)          |

|   | 3.1.21         | Receive Time Slot channel #2 (DRA2)32        |

|   | 3.1.22         | Receive Time Slot channel #3 (DRA3)32        |

|   | 3.1.23         | PCM Shift register (PCMSH) 33                |

|   | 3.1.24         | Interrupt Mask register for I/O port (DMASK) |

|   | 3.1.25         | Interrupt Mask register for CD port (CMASK)  |

|   | 3.1.26         | Persistency Check register (PCHK-A/B)35      |

|   | 3.1.27         | Interrupt register (INT)                     |

|   | 3.1.28         | Alarm register (ALARM)                       |

|   | 3.1.29         | Interrupt Mask register for Alarm (AMASK)    |

|   | 3.1.30         | Loopback register (LOOPB)                    |

|   | 3.1.31         | Transmit Preamplifier Gain register (TXG)    |

|   | 3.1.32         | Receive Amplifier Gain registers (RXG-10/32) |

|   | 3.1.33         | Silicon Revision Identification Code (SR=D)  |

| 4 | Application of | circuit                                      |

| 5 | Electrical ch  | aracteristics                                |

| 6 | Transmission   | n characteristics 46                         |

| 7 | Package info   | rmation                                      |

| 8 | Revision his   | tory                                         |

# List of tables

| Table 1. | Device summary                      |

|----------|-------------------------------------|

| Table 2. | I/O definition                      |

| Table 3. | Pin description                     |

| Table 4. | Control byte structure              |

| Table 5. | Registers addresses (only MCU mode) |

| Table 6. | Electrical characteristics          |

| Table 7. | Transmission characteristics        |

| Table 8. | Document revision history           |

57

# List of figures

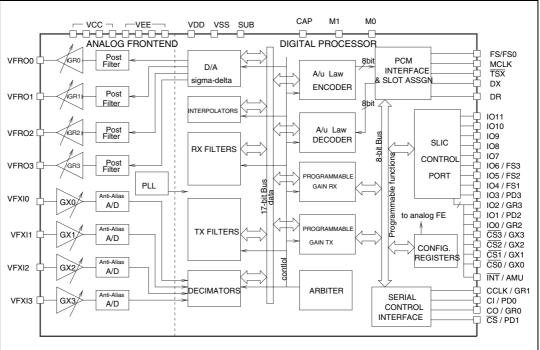

| Figure 1.  | Block diagram                                                                           | . 6 |

|------------|-----------------------------------------------------------------------------------------|-----|

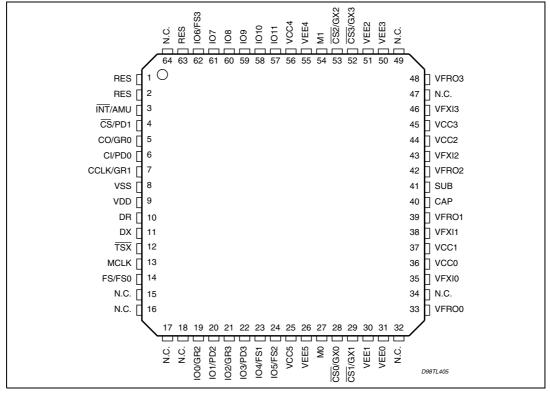

| Figure 2.  | Pin connection (top view)                                                               | . 6 |

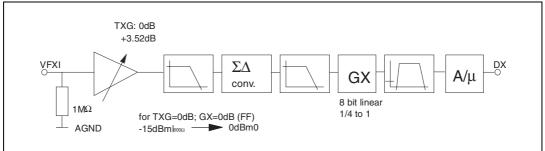

| Figure 3.  | Transmit path                                                                           | 13  |

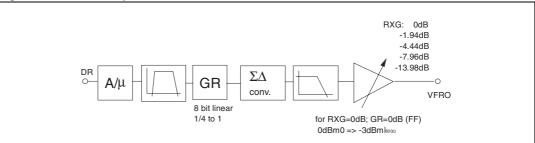

| Figure 4.  | Receive path                                                                            | 13  |

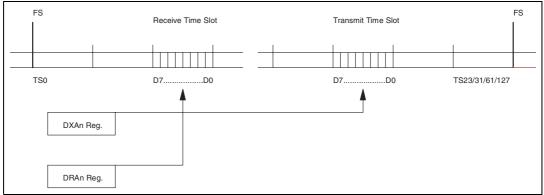

| Figure 5.  | MCU mode: time slot assignment                                                          | 13  |

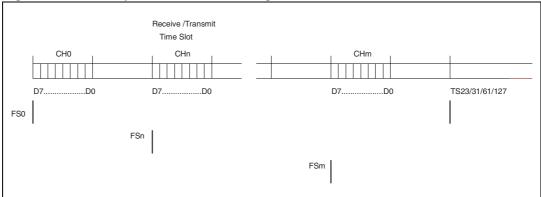

| Figure 6.  | Pin-strap mode: time slot assignment.                                                   | 15  |

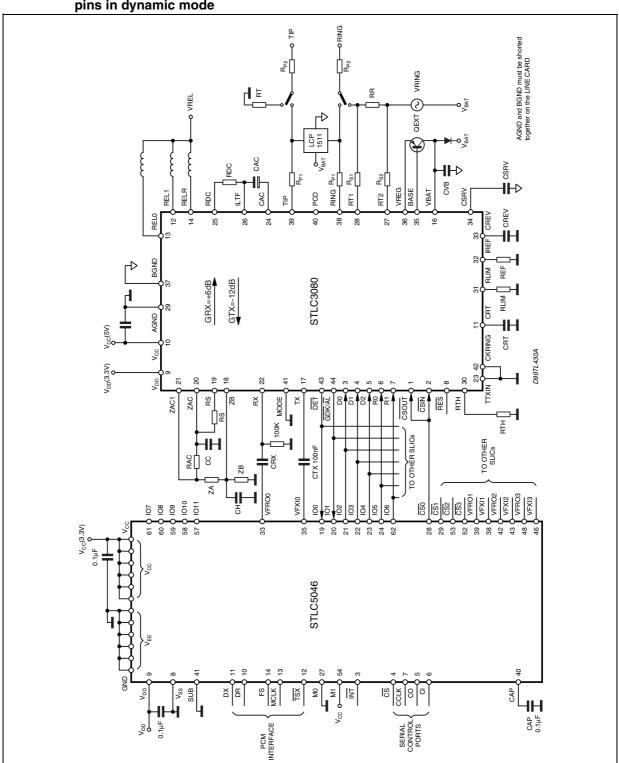

| Figure 7.  | Typical application circuit with STLC3080 without metering pulse injection and I/O pins |     |

|            | in dynamic mode                                                                         | 40  |

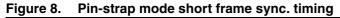

| Figure 8.  | Pin-strap mode short frame sync. timing                                                 | 43  |

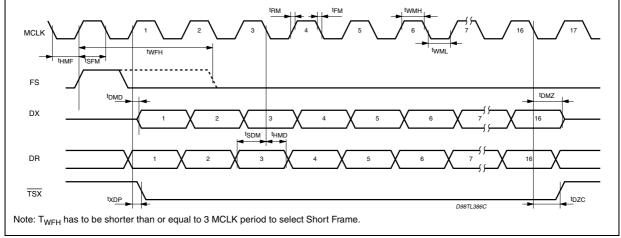

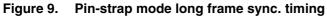

| Figure 9.  | Pin-strap mode long frame sync. timing                                                  | 44  |

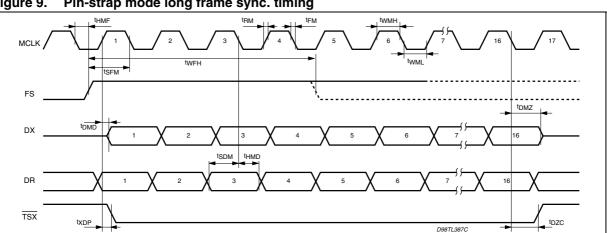

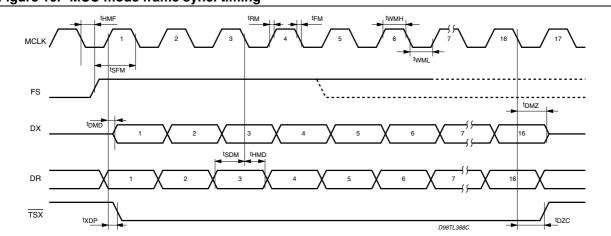

| Figure 10. | MCU mode frame sync. timing                                                             | 44  |

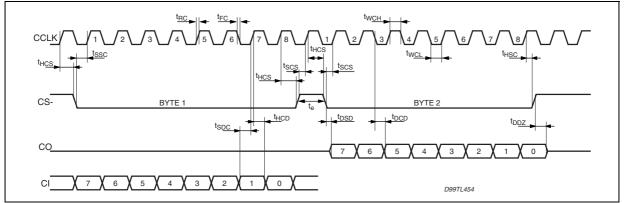

| Figure 11. | Serial control port timing                                                              | 44  |

| Figure 12. | SLIC control port timing                                                                | 45  |

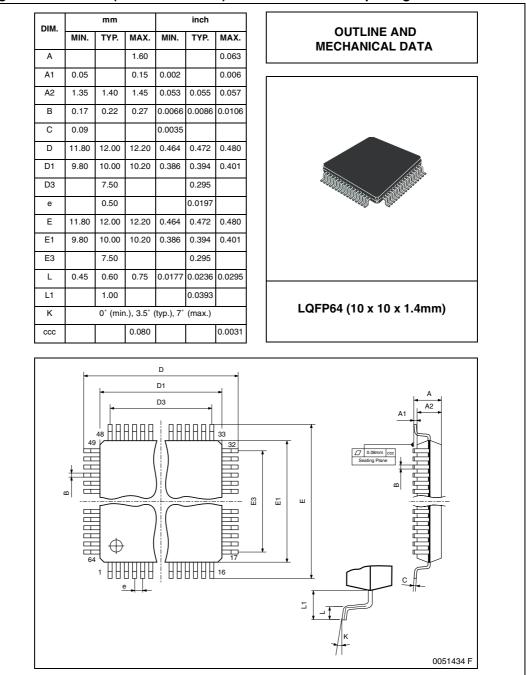

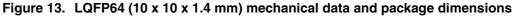

| Figure 13. | LQFP64 (10 x 10 x 1.4 mm) mechanical data and package dimensions                        | 49  |

# 1 Block diagram and pin connection

Doc ID 7052 Rev 5

# 1.1 Pin description

#### Table 2. I/O definition

| Туре | Definition              |  |  |  |

|------|-------------------------|--|--|--|

| AI   | Analog input            |  |  |  |

| AO   | Analog output           |  |  |  |

| ODO  | Open drain output       |  |  |  |

| DI   | Digital input           |  |  |  |

| DO   | Digital output          |  |  |  |

| DIO  | Digital input/output    |  |  |  |

| DTO  | Digital tristate output |  |  |  |

| DPS  | Digital power supply    |  |  |  |

| APS  | Analog power supply     |  |  |  |

#### Table 3.Pin description

| N.                            | Name                 | Туре | Function                                                                                                                                    |  |

|-------------------------------|----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Analog                        |                      |      |                                                                                                                                             |  |

| 33                            | VFRO0                | AO   | Receive analog amplifier output channel 0. PCM data received on the programmed time slot on DR input is decoded and appears at this output. |  |

| 39                            | VFRO1                | AO   | Receive analog amplifier output channel 1. PCM data received on the programmed time slot on DR input is decoded and appears at this output. |  |

| 42                            | VFRO2                | AO   | Receive analog amplifier output channel 2. PCM data received on the programmed time slot on DR input is decoded and appears at this output. |  |

| 48                            | VFRO3                | AO   | Receive analog amplifier output channel 3. PCM data received on the programmed time slot on DR input is decoded and appears at this output. |  |

| 35                            | VFXI0                | AI   | TX Input amplifier channel 0. Typ 1M.input impedance                                                                                        |  |

| 38                            | VFXI1                | AI   | TX Input amplifier channel 1. Typ 1M.input impedance                                                                                        |  |

| 43                            | VFXI2                | AI   | TX Input amplifier channel 2. Typ 1M.input impedance                                                                                        |  |

| 46                            | VFXI3                | AI   | TX Input amplifier channel 3. Typ 1M.input impedance                                                                                        |  |

| 40                            | CAP                  | AI   | AGND voltage filter pin. A 100nF capacitor must be connected between ground and this pin.                                                   |  |

| Power s                       | upply                |      |                                                                                                                                             |  |

| 25, 36,<br>37, 44,<br>45, 56, | VCC/0/1/2<br>/3/ 4/5 | APS  | Total 6 pins: 3.3 V analog power supplies, should be shorted together, require 100nF decoupling capacitor to VEE.                           |  |

| 26,30,<br>31, 50,<br>51,55    | VEE/0/1/2<br>/3/ 4/5 | APS  | Total 6 pins: analog ground, should be shorted together.                                                                                    |  |

| 9                             | VDD                  | DPS  | Digital power supply 3.3 V, require 100 nF decoupling capacitor to VSS.                                                                     |  |

| 8                             | VSS                  | DPS  | Digital ground                                                                                                                              |  |

| Table 3.                                       | Pin description (continued) |      |                                                                                                                                                                                                                                                                            |                                                                                                                                                                    |                                                                                                                                                     |  |  |

|------------------------------------------------|-----------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| N.                                             | Name                        | Туре | Function                                                                                                                                                                                                                                                                   |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 41                                             | SUB                         | DPS  | Substrate<br>possible                                                                                                                                                                                                                                                      |                                                                                                                                                                    | ction. Must be shorted together with VEE and VSS pins as close as $\cdot$                                                                           |  |  |

| Not conr                                       | lot connected               |      |                                                                                                                                                                                                                                                                            |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 15, 16,<br>17, 18,<br>32, 34,<br>47, 49,<br>64 | N.C.                        |      | Not connected.                                                                                                                                                                                                                                                             |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 1,2,63                                         | RES                         |      | Reserved                                                                                                                                                                                                                                                                   | d: must l                                                                                                                                                          | be left not connected.                                                                                                                              |  |  |

| Digital                                        |                             |      | 1                                                                                                                                                                                                                                                                          |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 27                                             | MO                          | DI   | Mode se                                                                                                                                                                                                                                                                    | ect, see                                                                                                                                                           | e M1                                                                                                                                                |  |  |

|                                                |                             |      | M1                                                                                                                                                                                                                                                                         | МО                                                                                                                                                                 | Mode select                                                                                                                                         |  |  |

| 54                                             | M1                          | DI   | 0<br>1<br>0<br>1                                                                                                                                                                                                                                                           | 1<br>0<br>0<br>1                                                                                                                                                   | Pin-strap mode: basic functions selected by proper pin strapping<br>MCU mode: device controlled via serial interface<br>Reset status<br>Not allowed |  |  |

| 13                                             | MCLK                        | DI   | Master clock input. Four possible frequencies can be used: 1.536/1.544 MHz; 2.048 MHz; 4.096 MHz; 8.192 MHz. The device automatically detect the frequency applied. This signal is also used as bit clock and it is used to shift data into and out of the DR and DX pins. |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 12                                             | TSX                         | ODO  | Transmit time slot (open drain output, 3.2mA). Normally it is floating in high impedance state except when a time slot is active on the DX output. In this case $\overline{TSX}$ output pulls low to enable the backplane line driver.                                     |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 11                                             | DX                          | DTO  | Transmit PCM interface. It remains in high impedance state except during the assigned time slots during which the PCM data byte is shifted out on the rising edge of MCLK.                                                                                                 |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 10                                             | DR                          | DI   |                                                                                                                                                                                                                                                                            | Receive PCM interface. It remains inactive except during the assigned receive time slots during which the PCM data byte is shifted in on the falling edge of MCLK. |                                                                                                                                                     |  |  |

| 61                                             | 107                         | DIO  | SLIC control I/O pin #7. Can be programmed as input or output via DIR register.<br>Depending on content of CONF register can be a static input/output or a dynamic<br>input/output synchronized with the CSn output signals controlling the SLICs.                         |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 60                                             | IO8                         | DIO  | SLIC control I/O pin #8. (see IO7 description).                                                                                                                                                                                                                            |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 59                                             | IO9                         | DIO  | SLIC control I/O pin #9. (see IO7 description).                                                                                                                                                                                                                            |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 58                                             | IO10                        | DIO  | SLIC control I/O pin #10. (see IO7 description).                                                                                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| 57                                             | IO11                        | DIO  | SLIC control I/O pin #11. (see IO7 description).                                                                                                                                                                                                                           |                                                                                                                                                                    |                                                                                                                                                     |  |  |

| Digital (c                                     | lual mode)                  |      |                                                                                                                                                                                                                                                                            |                                                                                                                                                                    |                                                                                                                                                     |  |  |

### Table 3. Pin description (continued)

| N. | Name    | Scriptio<br>Type | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|----|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|    |         | 78-              | MCU control mode: FS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 14 | FS/FS0  | DI               | Frame Sync. Pulse. A pulse or a square wave waveform with an 8kHz repetition<br>rate is applied to this pin to define the start of the receive and transmit frame.<br>Effective start of the frame can be then shifted of up to 7 clock pulses independed<br>in receive and transmit directions by proper programming of the PCMSH register<br>Pin-strap control mode: FS0.<br>Frame Sync. pulse of channel #0. One MCLK cycle long, starts PCM data trans-<br>in the Time Slot following its falling edge (Short Frame Delayed Timing). |  |  |

|    |         |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 19 | IO0/GR2 | DIO/DI           | MCU control mode: IO0.<br>Slic control I/O pin #0. Can be programmed as input or output via DIR register.<br>Depending on content of CONF register can be a static input/output or a dynamic<br>input/output synchronized with the CSn output signals controlling the SLICs.<br>Pin-strap control mode: GR2.<br>Receive gain programming channel 2:<br>1: Receive gain = -0.8 dB<br>0: Rec. gain = -4.3 dB                                                                                                                               |  |  |

| 20 | IO1/PD2 | DIO/DI           | MCU control mode: IO1.<br>Slic control I/O pin #1. (see IO0 description).<br>Pin-strap control mode: PD2.<br>Power Down command channel 2:<br>1: Channel 2 Codec is in power down.<br>(equivalent to CONF reg bit2 = 1)<br>0: Channel 2 Codec is in power up.<br>(equivalent to CONF reg. bit2 = 0)                                                                                                                                                                                                                                      |  |  |

| 21 | IO2/GR3 | DIO/DI           | MCU control mode: IO2.<br>Slic control I/O pin #2. (see IO0 description)<br>Pin-strap control mode: GR3.<br>Receive gain programming channel 3. (see GR2 description)                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 22 | IO3/PD3 | DIO/DI           | MCU control mode: IO3.<br>Slic control I/O pin #3. (see IO0 description).<br>Pin-strap control mode: PD3.<br>Power down command channel 3. (see PD2 description)                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 23 | IO4/FS1 | DIO/DI           | MCU control mode: IO4<br>Slic control I/O pin #4. (see IO0 description).<br>Pin-strap control mode: FS1.<br>Frame sync. pulse of channel #1. One MCLK cycle long, starts PCM data transfer in<br>the time slot following its falling edge (short frame delayed timing).                                                                                                                                                                                                                                                                  |  |  |

| 24 | IO5/FS2 | DIO/DI           | MCU control mode: IO4.<br>Slic control I/O pin #5. (see IO0 description).<br>Pin-strap control mode: FS2.<br>Frame sync. pulse of channel #1. One MCLK cycle long, starts PCM data transfer in<br>the time slot following its falling edge (short frame delayed timing).                                                                                                                                                                                                                                                                 |  |  |

#### Table 3. Pin description (continued)

| Table 3. | Pin description (continued) |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|----------|-----------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| N.       | Name                        | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

| 62       | IO6/FS3                     | DIO/DI | <ul> <li>MCU control mode: IO4.</li> <li>Slic control I/O pin #6. (see IO0 description).</li> <li>Pin-strap control mode: FS3.</li> <li>Frame sync. pulse of channel #1. One MCLK cycle long, starts PCM data transfer in the time slot following its falling edge (short frame delayed timing).</li> </ul>                                                                                                                                                                          |  |  |

| 28       | CS0/GX0                     | DO/DI  | MCU control mode: $\overline{CS0}$ .Slic CS control #0.Depending on CONF reg. content can be a CS output for SLIC #0 or a static I/O.When configured as CS output it is automatically generated by the Codec with a<br>repetition time of 31.25 $\mu$ s. In this mode also the IO11.0 are synchronized and carry<br>proper data in and out synchronous with CS.Pin-strap control mode:GX0.Transmit gain programming channel 0:1:Transmit gain = 0 dB<br>0:0:Transmit gain = - 3.5 dB |  |  |

| 29       | CS1/GX1                     | DO/DI  | MCU control mode: CS1:<br>Slic CS control #1, (see CS0 description).<br>Pin-strap control mode: GX1.<br>Transmit gain programming channel 1 (see GX0 description)                                                                                                                                                                                                                                                                                                                    |  |  |

| 53       | CS2/GX2                     | DO/DI  | MCU control mode: $\overline{\text{CS2}}$ .<br>Slic CS control #2, (see $\overline{\text{CS0}}$ description).<br>Pin-strap control mode: GX2.<br>Transmit gain programming channel 2 (see GX0 description)                                                                                                                                                                                                                                                                           |  |  |

| 52       | CS3/GX3                     | DO/DI  | MCU control mode: CS3.<br>Slic CS control #3, (see CS0 description).<br>Pin-strap control mode: GX3.<br>Transmit gain programming channel 3 (see GX0 description)                                                                                                                                                                                                                                                                                                                    |  |  |

| 4        | CS/PD1                      | DI/DI  | MCU control mode: $\overline{\text{CS}}$ .<br>Chip Select of Serial Control Bus. When this pin is low control information can be<br>written to or read from the device via the Cl and CO pins.<br>Pin-strap control mode: PD1.<br>Power Down command channel 1. (see PD2 description).                                                                                                                                                                                               |  |  |

| 7        | CCLK/GR1                    | DI/DI  | MCU control mode: CCLK.<br>Clock of Serial Control Bus. This clock shifts serial control information into or out of<br>CI or CO when CS input is low depending on the current instruction. CCLK may be<br>asynchronous with the other system clocks.<br>Pin-strap control mode: GR1.<br>Receive gain programming ch. 1, (see GR2 description).                                                                                                                                       |  |  |

| 6        | CI/PD0                      | DI/DI  | MCU control mode: CI.<br><u>Control Data Input of Serial Control Bus</u> . Control data is shifted in the device when<br><u>CS</u> is low and clocked by CCLK.<br>Pin-strap control mode: PD0.<br>Power Down command channel 0. (see PD2 description).                                                                                                                                                                                                                               |  |  |

Table 3.Pin description (continued)

Doc ID 7052 Rev 5

| N. | Name    | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|----|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 5  | CO/GR0  | DTO/DI | MCU control mode: CO.<br>Control Data Output of Serial Control Bus. Control data is shifted out the device<br>when $\overline{CS}$ is low and clocked by CCLK. During the first 8 CCLK pulses the CO pin is<br>H. I., valid data are shifted out during the following 8 CCLK pulses.<br>Pin-strap control mode: GR0.<br>Receive gain programming ch. 0, (see GR2 description). |  |  |

| 3  | ĪNT/AMU | ODO/DI | MCU control mode: $\overline{INT}$ .<br>Interrupt output (open drain), goes low when a data change has been detected in<br>the I/O pins. One mask registers allow to mask any I/O pin. Interrupt is reset when<br>the I/O register is read.<br>Pin-strap control mode: AMU.<br>A/µ Law selection:<br>AMU=0: µ Law<br>AMU=1: A Law, even bit inverted                           |  |  |

### Table 3. Pin description (continued)

# 2 Functional description

### 2.1 Power on initialization

When power is first applied it is recommended to reset the device by forcing the condition M1.0=00, in order to clear all the internal registers.

In MCU mode M0 is set steadily Low and the device is reset by applying a negative pulse to M1 (its operative level in MCU mode is High); same result can be obtained by writing an High level into the control bit RES of the CONF register.

In pin-strap mode M1 is set steadily Low and the device is reset by applying a negative pulse to M0 (its operative level in pin-strap mode is High); at the end of the Reset phase (M0=High) the device is programmed according to the logical configuration of the control pins.

During the reset condition all the I/On and CS\_n pins are set as inputs, DX is set in high impedance and all VFROn outputs are forced to AGND.

# 2.2 Power down state

Each of the four channel may be put into power down mode by setting the appropriate bit in the CONF register or strapping to VDD the proper pin. In this mode the eventual programmed DX channel is set in high impedance while the VFRO outputs are forced to AGND. In pin-strap mode the value forced on the input pin is internally updated every FS signal.

# 2.3 Transmit path

The analog VFXI signal through an amplifier stage is applied to a PCM converter and the corresponding digital signal is sent to DX output.

In MCU mode, the amplifier gain can be programmed with two different values by means of TXG Reg.: 0 dB or +3.52 dB.

A programmable gain block after the A/D conversion allows to set transmit gain in 12dB range, with steps <0.1dB by writing proper code into GTXn register.

Setting GTXn=00h, the transmitted signal is muted, i.e. an idle PCM signal is generated on DX.

A/ $\mu$  coding Law is selected by bit5 (AMU) of CONF reg.

Setting LIN=1 (bit6 of CONF reg.) the linear coding Law is selected (16bits); in this case the signal sent on DX will take two adjacent PCM time slots.

In Pin-strap mode, the amplifier gain is set to 0dB; only two values of Transmit gain can be selected according to the level of GXn control input (in Pin-strap):

GXn=1 selects the gain corresponding to GTXn=FFh (0 dB)

GXn=0 selects the gain corresponding to GTXn=8Fh (-3.5 dB)

Different gain value is obtained through proper voltage divider.

A/µ coding Law is selected according to AMU pin level:

AMU=0 µ Law selected.

AMU=1 A Law selected.

VFXI input must be AC coupled to the signal source; the voltage swing allowed is 1.0Vpp when the preamplifier gain is set 0dB or 0.66Vpp if the gain is set to 3.52dB (MCU mode only); higher levels must be reduced through proper dividers.

Typical impedance of VFXI input is 1Mohm.

Figure 3. Transmit path

#### Figure 4. Receive path

#### Figure 5. MCU mode: time slot assignment

# 2.4 Receive path

The received PCM signal DR through the decoder section, the gain select block and the D/A converter is converted in an analog signal which is transferred to VFRO output through an amplifier stage.

Doc ID 7052 Rev 5

In MCU mode a programmable gain block before the A/D conversion allows to set receive gain in 12dB range, with steps <0.1 dB by writing proper code into GRXn register.

The amplifier gain can be programmed with five different values by means of RXG register: 0 dB -1.94 dB -4.44 dB -7.96 dB -13.98 dB.

Setting GRXn=00h, the receive signal is muted and VFRO output is set to AGND.

$A/\mu$  coding Law is selected by bit5 (AMU) of CONF reg.

Setting LIN = 1 (bit6 of CONF reg.) the linear coding Law is selected (16bits); in this case the signal received on DR will take two adjacent PCM time slots.

In pin-strap mode only two values of Receive Gain can be selected according to the level of GRn control input (in pin-strap) GRn = 1 selects the gain corresponding to GRXn = E2h, RXG = 0dB (-0.8 dB) GRn = 0 selects the gain corresponding to GRXn = AFh, RXG = -1.94 dB (-4.3 dB).

Different gain value is obtained through proper voltage divider.

A/µ coding Law is selected according to AMU pin level:

AMU=0 µ Law selected.

AMU=1 A Law selected.

VFRO output, referred to AGND must be AC coupled to the load, referred to VSS, to prevent a DC current flow.

VFRO has a drive capability of 1.0mA (peak value), with a max AC swing of 2 Vpp.

In order to get the best noise performances it is recommended to keep the GRX value as close as possible to the maximum (FFh) setting properly the additional attenuation by means of RXG.

# 2.5 PCM interface

The STLC5046 dedicate five pins (six in pin-strap mode) to the interface with the PCM highways.

MCLK represents the bit clock and is also used by the device as a source for the clock of the internal Sigma Delta converter timings. Four possible frequencies can be used: 1.536/1.544 MHz (24 channels PCM frame); 2048 MHz (32 channels PCM frame); 4.096 MHz (64 channels PCM frame); 8.192 MHz (128 channels PCM frame).

The operating frequency is automatically detected by the device when both MCLK and FS are applied. MCLK is synchronizing both the transmit data (DX) and the receive data (DR).

#### 2.5.1 MCU mode

The Frame Sync. signal FS is the common time base for all the four channels; Short (one MCLK period) or Long (more than one MCLK period) FS are allowed.

Transmit and Receive programmable Time-Slots are framed to an internal sync. signal that can be coincident with FS or delayed of 1 to 7 MCLK cycles depending on the programming of PCMSH register.

DX represent the transmit PCM interface. It remains in high impedance state except during the assigned time slots during which the PCM data byte is shifted out on the rising edge of MCLK.

The four channels can be shifted out in any possible timeslot as defined by the DXA0 to DXA3 registers. If one codec is set in Power Down by software programming the corresponding timeslot is set in High Impedance. When linear coding mode is selected by CONF register programming the output channel will need two consecutive timeslots (see register description).

DR represent the receive PCM interface. It remains inactive except during the assigned time

slots during which the PCM data byte is shifted in on the falling edge of MCLK. The four channels are shifted in any possible timeslot as defined by the DRA0 to DRA3 registers.

Figure 6. Pin-strap mode: time slot assignment

#### 2.5.2 Pin-strap mode

When pin-strap mode is selected, dedicated Frame Sync. FS3..0 are provided on dual function pins:

| MCU | Pin-strap | Pin |

|-----|-----------|-----|

| FS  | FS0       | 14  |

| IO4 | FS1       | 23  |

| IO5 | FS2       | 24  |

| IO6 | FS3       | 62  |

The PCMSH register cannot be accessed, therefore the beginning of the transmit and receive frame is identified by the rising edge of the FSn signal.

Each channel has its dedicated Frame Sync. signal FSn. Short or Long frame timing is automatically selected; depending on the FS signal applied to FS0 input. The assigned Time Slot (Transmit and Receive) takes place in the 8 MCLK cycles following the falling edge of FSn in case of Short Frame or the rising edge in case of Long Frame. If one codec is set in Power Down by proper pin-strap configuration the corresponding timeslot is not loaded and the VFRO output is kept at steady AGND level.

Finally by means of the LOOPB register is possible to implement a digital or analog loop\_back on any of the selected channels.

TSX represent the Transmit Time Slot (open drain output, 3.2mA). Normally it is floating in high impedance state except when a time slot is active on the DX output. In this case TSX output pulls low to enable the backplane line driver. Should be strapped to VSS when not used.

| First byte (address) |     |    |    |    |    |    |    |  |

|----------------------|-----|----|----|----|----|----|----|--|

| 7                    | 6   | 5  | 4  | 3  | 2  | 1  | 0  |  |

| R/W                  | D/S | A5 | A4 | A3 | A2 | A1 | A0 |  |

| D7                   | D6  | D5 | D4 | D3 | D2 | D1 | D0 |  |

Table 4.Control byte structure

$R/\overline{W} = 0$ : Write register

$R/\overline{W} = 1$ : Read register

$D/\overline{S} = 0$ : Single byte

$D/\overline{S} = 1$ : Two bytes

A5..A0: Register Address

# 2.6 Control interface

STLC5046 has two control modes, a microprocessor control mode and a pin-strap control mode. The two modes are selected by M0 and M1 pins. When M0 = low, M1 = high (MCU control mode) the MCU port is activated; and the 41 registers of the device can be programmed. When M0 = high, M1 = low (Pin-strap mode) the microprocessor control port is disabled and some of the digital pins change their function allowing to perform a very basic programming of the device.

In pin-strap mode the status of the control pins is entered at power-on reset and refreshed at any Frame Sync. cycle.

In MCU mode the control information is written to or read from STLC5046 via the serial four wires control bus:

CCLK: Control Clock

CS: Chip Select input

- CI: Serial Data input

- CO: Serial Data output

All control instructions require 2 bytes, with the exception of the single byte for command synchronization. The first byte specify the register address, and the type of access (Read or Write). The second byte contain the data to be loaded into the register (on CI wire) or carried out the register content (on CO wire) depending on the R/W bit of the first byte. CO wire is normally in High Impedance and goes to low impedance only during the second byte in case of Read operation. This allows to use a common wire for both CI/CO.

Serial data CI is shifted to the serial input register on the rising edge of CCLK and CO is shifted out on the falling.

CS, normally High, is set Low during the transmission / reception of a byte, lasting 8CCLK pulses.

Though, in general, two bytes of the same instruction take two  $\overline{CS}$  separated cycles, STLC5046 can handle the data transfer in a single 16 CCLK CS cycle, in both the directions.

One additional wire provided to the control interface is an open drain interrupt output (INT) that goes low when a change of status is detected on the I/O pins.

### 2.7 SLIC control interface

The device provides 12 I/O pins plus 4  $\overline{CS}$  signals. The interface can work in dynamic or static mode: it can be selected by means of DIR register.

- Dynamic Mode: the I/O pins are configured as input or output by means of DIR register. The CS signals are used to select the different SLIC interface. In this case the I/O pin can be multiplexed. The data loaded from SLIC#n via I/O pins configured as input can be read in the DATAn register. The data written in a DATAn register will be loaded on the I/O pins configured as output when the Csn signal will be active.

- Static Mode: The CS signal can be used as I/O pins. They can be configured as input or output I/O by means of DATA1 register. The data corresponding to the CS signal can be read or written by means of DATA2 register. All data related to th other I/O pins can be read or written by means of DATA0 register.

# 3 Registers addresses

| AddressNameDescription00hCONFConfiguration register01hDIR-LI/O Direction (bit 7-0)02hDIR-HI/O Direction (bit 11-8)03hDATA0-LI/O Data ch#0/ Static Data; (bit 7-0)04hDATA0-HI/O Data ch#0/ Static Data; (bit 11-8)05hDATA1-LI/O Data ch#1 (bit 7-0) / CS Direction06hDATA1-HI/O Data ch#1 (bit 11-8)07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX3Transmit Gain ch#3      |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 01hDIR-LI/O Direction (bit 7-0)02hDIR-HI/O Direction (bit 11-8)03hDATA0-LI/O Data ch#0/ Static Data; (bit 7-0)04hDATA0-HI/O Data ch#0/ Static Data; (bit 11-8)05hDATA1-LI/O Data ch#1 (bit 7-0) / CS Direction06hDATA1-HI/O Data ch#1 (bit 7-0) / CS Direction06hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#3 (bit 7-0)0AhDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#3 |  |

| 02hDIR-HI/O Direction (bit 11-8)03hDATA0-LI/O Data ch#0/ Static Data; (bit 7-0)04hDATA0-HI/O Data ch#0/ Static Data; (bit 11-8)05hDATA1-LI/O Data ch#1 (bit 7-0) / CS Direction06hDATA1-HI/O Data ch#1 (bit 11-8)07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#3                                                                                        |  |

| 03hDATA0-LI/O Data ch#0/ Static Data; (bit 7-0)04hDATA0-HI/O Data ch#0/ Static Data; (bit 11-8)05hDATA1-LI/O Data ch#1 (bit 7-0) / CS Direction06hDATA1-HI/O Data ch#1 (bit 11-8)07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX3Transmit Gain ch#3                                                                                                                        |  |

| 04hDATA0-HI/O Data ch#0/ Static Data; (bit 11-8)05hDATA1-LI/O Data ch#1 (bit 7-0) / CS Direction06hDATA1-HI/O Data ch#1 (bit 11-8)07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#3                                                                                                                                                                       |  |

| 05hDATA1-LI/O Data ch#1 (bit 7-0) / CS Direction06hDATA1-HI/O Data ch#1 (bit 11-8)07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#3                                                                                                                                                                                                                       |  |

| 06hDATA1-HI/O Data ch#1 (bit 11-8)07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#20EhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                              |  |

| 07hDATA2-LI/O Data ch#2 (bit 7-0) / CS Data08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#20EhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                |  |

| 08hDATA2-HI/O Data ch#2 (bit 11-8)09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#20EhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                           |  |

| 09hDATA3-LI/O Data ch#3 (bit 7-0)0AhDATA3-HI/O Data ch#3 (bit 11-8)0BhGTX0Transmit Gain ch#00ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#20EhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                                                             |  |

| OAhDATA3-HI/O Data ch#3 (bit 11-8)OBhGTX0Transmit Gain ch#0OChGTX1Transmit Gain ch#1ODhGTX2Transmit Gain ch#2OEhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                                                                                              |  |

| OBhGTX0Transmit Gain ch#0OChGTX1Transmit Gain ch#1ODhGTX2Transmit Gain ch#2OEhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| 0ChGTX1Transmit Gain ch#10DhGTX2Transmit Gain ch#20EhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 0DhGTX2Transmit Gain ch#20EhGTX3Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 0Eh GTX3 Transmit Gain ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 0Fh GRX0 Receive Gain ch#0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 10h GRX1 Receive Gain ch#1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 11h GRX2 Receive Gain ch#2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 12h GRX3 Receive Gain ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 13h DXA0 Transmit Timeslot ch#0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 14h DXA1 Transmit Timeslot ch#1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 15h DXA2 Transmit Timeslot ch#2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 16h DXA3 Transmit Timeslot ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| 17h DRA0 Receive Timeslot ch#0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 18h DRA1 Receive Timeslot ch#1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 19h DRA2 Receive Timeslot ch#2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 1Ah DRA3 Receive Timeslot ch#3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| 1Bh PCMSH PCM Shift register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| 1Ch DMASK-L Interrupt Mask I/O Port (03h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 1Dh DMASK-H Interrupt Mask I/O Port (04h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| 1Eh CMASK Interrupt Mask I/O Port (07h)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| 1Fh PCHK-A Persistency Check Time for Input A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 20h PCHK-B Persistency Check Time for Input B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 21h INT Interrupt register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 22h ALARM Alarm register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| 23h AMASK Interrupt Mask for Alarm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 24h LOOPB Loopback register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 25h TXG Transmit Preamp. Gain                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 26h RXG-1,0 Receive Preamp. Gain (ch1 ch0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 27h RXG-3,2 Receive Preamp. Gain (ch3 ch2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| 31h SRID Silicon Revision Identification Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

Table 5.

Registers addresses (only MCU mode)

# 3.1 Registers description

#### 3.1.1 Configuration register (CONF)

Addr=00h; Reset Value=3Fh

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| RES  | LIN  | AMU  | STA  | PD3  | PD2  | PD1  | PD0  |

**RES=0** Normal operation

RES=1 Device reset: I/On and CSn are all inputs, DX is H.I. (equivalent to Hw. reset).

LIN=0 A or µ Law PCM encoding

LIN=1 Linear encoding (16 bits), two's complement.

AMU=0 µ Law selection

AMU=1 A Law selection (even bits inverted)

STA=0  $\overline{CS0}$  to  $\overline{CS3}$  scan the four SLICs connected to the I/O control port, each  $\overline{CS}$  has a 31.25µs repetition time.

STA=1; I/O are static,  $\overline{CS0}$  to  $\overline{CS3}$  are configured as generic static I/O

PD3..0=0 CODEC 3..0 is active

PD3..0=1 CODEC 3..0 is in power Down. When one codec is in Power Down the corresponding VFRO output is forced to AGND. and the corresponding transmit time slot on DX is set in H.I.

Pin-strap value:

| RES 0 | AMU | 0 | PD3 | PD2 | PD1 | PD0 |

|-------|-----|---|-----|-----|-----|-----|

|-------|-----|---|-----|-----|-----|-----|

#### 3.1.2 I/O Direction register (DIR)

Addr=01h; Reset Value=00h

Addr=02h; Reset Value=X0h

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0            |

|------|------|------|------|------|------|------|-----------------|

| IO7  | IO6  | IO5  | IO4  | IO3  | IO2  | IO1  | IO <sub>0</sub> |

|      |      |      |      | IO11 | IO10 | IO9  | IO8             |

$IO_{11..0} = 0$ ; I/O pin 11..0 is an input, data on the I/O input is written in DATAn register bit 11..0.

$IO_{11..0} = 1$ ; I/O pin 11..0 is an output, data contained in DATAn register bit11..0 is transferred to the I/O output.

Pin-strap value:

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

#### 3.1.3 I/O Data register channel #0 (DATA0)

Addr=03h; Reset Value=00h Addr=04h; Reset Value=X0h If bit 4 of CONF register (STA)=0 Dynamic I/O mode:

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|

| D07  | D06  | D05  | D04  | D03  | D02  | D01  | D00  |

|      |      |      |      | D011 | D010 | D09  | D08  |

When  $\overline{CS0}$  is active D011..0 are transferred to the corresponding I/O pins configured as outputs (see DIR register). For the I/O pins configured as inputs the corresponding D011..0 will be written by the values applied to those pins while CS0 is low.

If bit 4 of CONF register (STA)=1

Static I/O mode:

| Bit7 | Bit6 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|------|------|------|------|------|------|------|------|