# **Precision Low Power Single-Supply JFET Amplifier**

## AD8627/AD8626/AD8625

#### **FEATURES**

SC70 package

Very low IB: 1 pA max

Single-supply operation: 5 V to 26 V Dual-supply operation: ±2.5 V to ±13 V

Rail-to-rail output

Low supply current: 630 µA/amp typ Low offset voltage: 500 µV max

Unity gain stable No phase reversal

#### **APPLICATIONS**

**Photodiode amplifiers**

**ATE**

Line-powered/battery-powered instrumentation Industrial controls **Automotive sensors Precision filters Audio**

#### **GENERAL DESCRIPTION**

The AD862x is a precision JFET input amplifier. It features true single-supply operation, low power consumption, and rail-to-rail output. The outputs remain stable with capacitive loads of over 500 pF; the supply current is less than 630 μA/amp. Applications for the AD862x include photodiode transimpedance amplification, ATE reference level drivers, battery management, both line powered and portable instrumentation, and remote sensor signal conditioning including automotive sensors.

The AD862x's ability to swing nearly rail-to-rail at the input and rail-to-rail at the output enables it to be used to buffer CMOS DACs, ASICs, and other wide output swing devices in single-supply systems.

The 5 MHz bandwidth and low offset are ideal for precision

The AD862x is fully specified over the industrial temperature range. (-40° to +85°) The AD8627 is available in both 5-lead SC70 and 8-lead SOIC surface-mount packages. The SC70 packaged parts are available in tape and reel only. The AD8626 is available in an MSOP package.

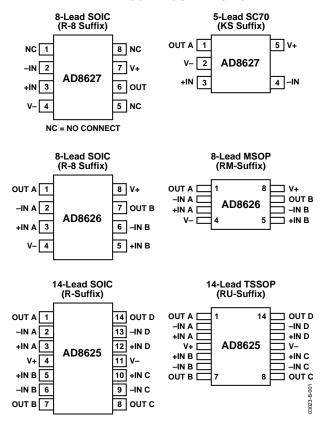

#### PIN CONFIGURATIONS

Fiaure 1.

### **TABLE OF CONTENTS**

| AD8627/AD8626/AD8625–Specifications                       |

|-----------------------------------------------------------|

| Electrical Characteristics                                |

| Electrical Characteristics                                |

| Absolute Maximum Ratings                                  |

| Typical Performance Characteristics– AD8627/AD8626/AD8625 |

| Applications                                              |

| REVISION HISTORY                                          |

| 1/04—Data sheet changed from Rev. A to Rev. B             |

| Change to General Description                             |

| 10/03—Data sheet changed from Rev. 0 to Rev. A            |

| Addition of two new partsUniversal                        |

| Change to General Description1                            |

| Changes to Pin Configurations1                            |

| Change to Specifications table                            |

| Changes to Figure 3110                                    |

| Changes to Figure 3211                                    |

| Changes to Figure 3812                                    |

| Changes to Figure 4616                                    |

| Changes to Figure 47                                      |

| Changes to Figure 49                                      |

| Updated Outline Dimensions                                |

| Changes to Ordering Guide                                 |

| Mi    | inimizing Input Current                          | 15 |

|-------|--------------------------------------------------|----|

| Ph    | otodiode Preamplifier Application                | 15 |

| Ou    | atput Amplifier for Digital-to-Analog Converters | 15 |

| Eig   | ght-Pole Sallen Key Low-Pass Filter              | 16 |

| Outli | ine Dimensions                                   | 18 |

| Or    | dering Guide                                     | 19 |

## AD8627/AD8626/AD8625-SPECIFICATIONS

#### **ELECTRICAL CHARACTERISTICS**

Table 1. @ $V_S = 5$  V,  $V_{CM} = 1.5$  V,  $T_A = 25$ °C, unless otherwise noted.

| Parameter                    | Symbol                   | Conditions                                                            | Min  | Тур  | Max   | Unit    |

|------------------------------|--------------------------|-----------------------------------------------------------------------|------|------|-------|---------|

| INPUT CHARACTERISTICS        |                          |                                                                       |      |      |       |         |

| Offset Voltage               | Vos                      |                                                                       |      | 0.05 | 0.5   | mV      |

|                              |                          | -40°C < T <sub>A</sub> < +85°C                                        |      |      | 1.2   | mV      |

| Input Bias Current           | I <sub>B</sub>           |                                                                       |      | 0.25 | 1     | pА      |

|                              |                          | -40°C < T <sub>A</sub> < +85°C                                        |      |      | 60    | pA      |

| Input Offset Current         | los                      |                                                                       |      |      | 0.5   | pА      |

|                              |                          | -40°C < T <sub>A</sub> < +85°C                                        |      |      | 25    | рА      |

| Input Voltage Range          |                          |                                                                       | 0    |      | 3     | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = 0 \text{ V to } 2.5 \text{ V}$                              | 66   | 87   |       | dB      |

| Large Signal Voltage Gain    | Avo                      | $R_L = 10 \text{ k}\Omega$ , $v_0 = 0.5 \text{ V to } 4.5 \text{ V}$  | 100  | 230  |       | V/mV    |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ | -40°C < T <sub>A</sub> < +85°C                                        |      | 2.5  |       | μV/°C   |

| OUTPUT CHARACTERISTICS       |                          |                                                                       |      |      |       |         |

| Output Voltage High          | $V_{OH}$                 |                                                                       | 4.92 |      |       | V       |

|                              |                          | $I_L = 2 \text{ mA}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ | 4.90 |      |       | V       |

| Output Voltage Low           | $V_{OL}$                 |                                                                       |      |      | 0.075 | V       |

|                              |                          | $I_L = 2 \text{ mA}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ |      |      | 0.08  | V       |

| Output Current               | l <sub>OUT</sub>         |                                                                       |      | ±10  |       | mA      |

| POWER SUPPLY                 |                          |                                                                       |      |      |       |         |

| Power Supply Rejection Ratio | PSRR                     | $V_S = 5 \text{ V to } 26 \text{ V}$                                  | 80   | 104  |       | dB      |

| Supply Current/Amplifier     | I <sub>SY</sub>          |                                                                       |      | 630  | 785   | μΑ      |

|                              |                          | $-40^{\circ}\text{C} < \text{T}_{A} < +85^{\circ}\text{C}$            |      |      | 800   | μΑ      |

| DYNAMIC PERFORMANCE          |                          |                                                                       |      |      |       |         |

| Slew Rate                    | SR                       |                                                                       |      | 5    |       | V/µs    |

| Gain Bandwidth Product       | GBP                      |                                                                       |      | 5    |       | MHz     |

| Phase Margin                 | Øм                       |                                                                       |      | 60   |       | Degrees |

| NOISE PERFORMANCE            |                          |                                                                       |      |      |       |         |

| Voltage Noise                | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                       |      | 1.9  |       | μV p-p  |

| Voltage Noise Density        | e <sub>n</sub>           | f = 1 kHz                                                             |      | 17.5 |       | nV/√Hz  |

| Current Noise Density        | İn                       | f = 1 kHz                                                             |      | 0.4  |       | fA/√Hz  |

| Channel Separation           | Cs                       | f = 1 kHz                                                             |      | 104  |       | dB      |

#### **ELECTRICAL CHARACTERISTICS**

Table 2. @ $V_S = \pm 13 \text{ V}$ ;  $V_{CM} = 0 \text{ V}$ ;  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted.

| Parameter                    | Symbol                   | Conditions                                                            | Min    | Тур  | Max    | Unit    |

|------------------------------|--------------------------|-----------------------------------------------------------------------|--------|------|--------|---------|

| INPUT CHARACTERISTICS        |                          |                                                                       |        |      |        |         |

| Offset Voltage               | Vos                      |                                                                       |        | 0.35 | 0.75   | mV      |

|                              |                          | -40°C < T <sub>A</sub> < +85°C                                        |        |      | 1.35   | mV      |

| Input Bias Current           | I <sub>B</sub>           |                                                                       |        | 0.25 | 1      | pА      |

|                              |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$     |        |      | 60     | pА      |

| Input Offset Current         | los                      |                                                                       |        |      | 0.5    | рA      |

|                              |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$     |        |      | 25     | pА      |

| Input Voltage Range          |                          |                                                                       | -13    |      | +11    | V       |

| Common-Mode Rejection Ratio  | CMRR                     | $V_{CM} = -13 \text{ V to } +10 \text{ V}$                            | 76     | 105  |        | dB      |

| Large Signal Voltage Gain    | Avo                      | $R_L = 10 \text{ k}\Omega$ , $V_O = -11 \text{ V to } +11 \text{ V}$  | 150    | 310  |        | V/mV    |

| Offset Voltage Drift         | $\Delta V_{OS}/\Delta T$ | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$     |        | 2.5  |        | μV/°C   |

| OUTPUT CHARACTERISTICS       |                          |                                                                       |        |      |        |         |

| Output Voltage High          | V <sub>он</sub>          |                                                                       | +12.92 |      |        | V       |

|                              | V <sub>OH</sub>          | $I_L = 2 \text{ mA}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ | +12.91 |      |        | V       |

| Output Voltage Low           | VoL                      |                                                                       |        |      | -12.92 | V       |

|                              | V <sub>OL</sub>          | $I_L = 2 \text{ mA}, -40^{\circ}\text{C} < T_A < +85^{\circ}\text{C}$ |        |      | -12.91 | V       |

| Output Current               | Іоит                     |                                                                       |        | ±15  |        | mA      |

| POWER SUPPLY                 |                          |                                                                       |        |      |        |         |

| Power Supply Rejection Ratio | PSRR                     | $V_S = \pm 2.5 \text{ V to } \pm 13 \text{ V}$                        | 80     | 104  |        | dB      |

| Supply Current/Amplifier     | I <sub>SY</sub>          |                                                                       |        | 710  | 850    | μΑ      |

|                              |                          | $-40^{\circ}\text{C} < \text{T}_{\text{A}} < +85^{\circ}\text{C}$     |        |      | 900    | μΑ      |

| DYNAMIC PERFORMANCE          |                          |                                                                       |        |      |        |         |

| Slew Rate                    | SR                       |                                                                       |        | 5    |        | V/µs    |

| Gain Bandwidth Product       | GBP                      |                                                                       |        | 5    |        | MHz     |

| Phase Margin                 | Ø <sub>M</sub>           |                                                                       |        | 60   |        | Degrees |

| NOISE PERFORMANCE            |                          |                                                                       |        |      |        |         |

| Voltage Noise                | e <sub>n</sub> p-p       | 0.1 Hz to 10 Hz                                                       |        | 2.5  |        | μV p-p  |

| Voltage Noise Density        | e <sub>n</sub>           | f = 1 kHz                                                             |        | 16   |        | nV/√Hz  |

| Current Noise Density        | İn                       | f = 1 kHz                                                             |        | 0.5  |        | fA/√Hz  |

| Channel Separation           | Cs                       | f = 1 kHz                                                             |        | 105  |        | dB      |

#### **ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Absolute maximum ratings apply at 25°C, unless otherwise noted.

**Table 3. Stress Ratings**

| Parameter                                  | Rating               |

|--------------------------------------------|----------------------|

| Supply Voltage                             | 27 V                 |

| Input Voltage                              | $V_{S-}$ to $V_{S+}$ |

| Differential Input Voltage                 | ± Supply Voltage     |

| Output Short Circuit Duration              | Indefinite           |

| Storage Temperature Range, R Package       | −65°C to + 125°C     |

| Operating Temperature Range                | −40°C to + 85°C      |

| Junction Temperature Range, R Package      | −65°C to 150°C       |

| Lead Temperature Range (Soldering, 60 sec) | 300°C                |

Table 4.

| Package Type       | $\theta_{JA}$ 1 | <b>Ө</b> лс | Unit |

|--------------------|-----------------|-------------|------|

| 5-Lead SC70 (KS)   | 376             | 126         | °C/W |

| 8-Lead MSOP (RM)   | 210             | 45          | °C/W |

| 8-Lead SOIC (R)    | 158             | 43          | °C/W |

| 14-Lead SOIC (R)   | 120             | 36          | °C/W |

| 14-Lead TSSOP (RU) | 180             | 35          | °C/W |

$<sup>^{1}</sup>$   $\theta_{JA}$  is specified for worst case conditions when devices are soldered in circuit boards for surface-mount packages.

#### **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### TYPICAL PERFORMANCE CHARACTERISTICS—AD8627/AD8626/AD8625

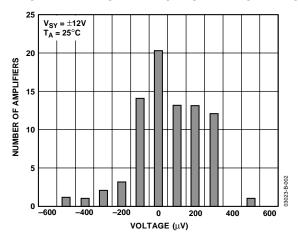

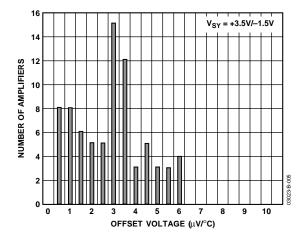

Figure 2. Input Offset Voltage

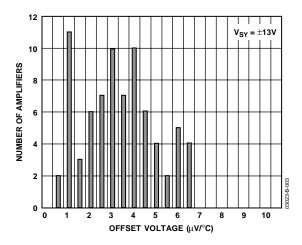

Figure 3. Offset Voltage Drift

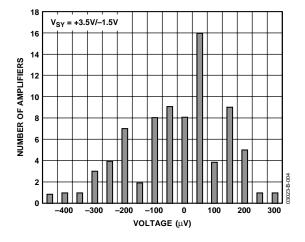

Figure 4. Input Offset Voltage

Figure 5. Offset Voltage Drift

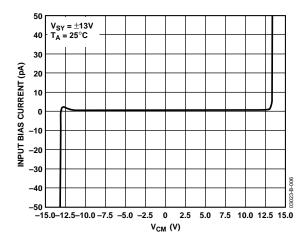

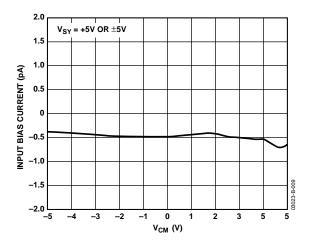

Figure 6. Input Bias Current vs. V<sub>CM</sub>

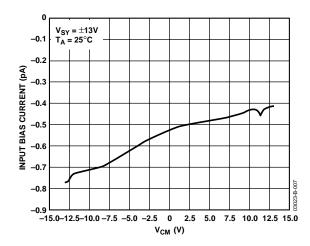

Figure 7. Input Bias Current vs. V<sub>CM</sub>

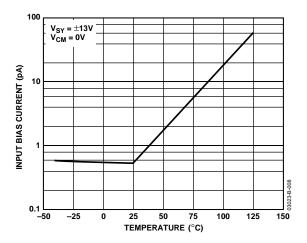

Figure 8. Input Bias Current vs. Temperature

Figure 9. Input Bias Current vs. V<sub>CM</sub>

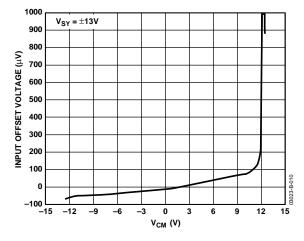

Figure 10. Input Offset Voltage vs. V<sub>CM</sub>

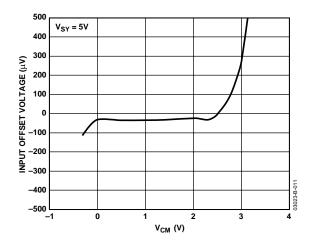

Figure 11. Input Offset Voltage vs. V<sub>CM</sub>

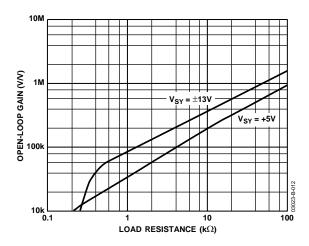

Figure 12. Open-Loop Gain vs. Load Resistance

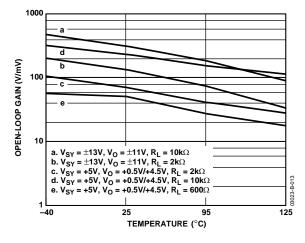

Figure 13. Open-Loop Gain vs. Temperature

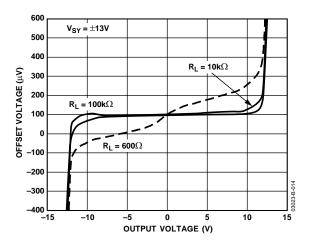

Figure 14. Input Error Voltage vs. Output Voltage for Resistive Loads

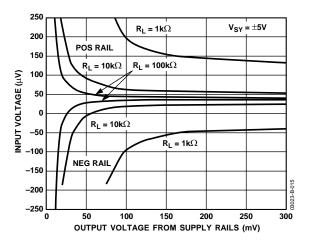

Figure 15. Input Error Voltage vs. Output Voltage within 300 mV of Supply Rails

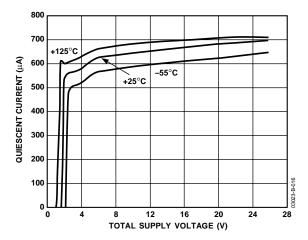

Figure 16. Quiescent Current vs. Supply Voltage at Different Temperatures

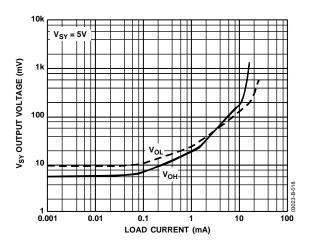

Figure 17. Output Saturation Voltage vs. Load Current

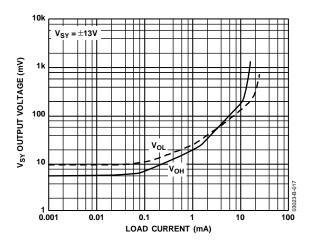

Figure 18. Output Saturation Voltage vs. Load Current

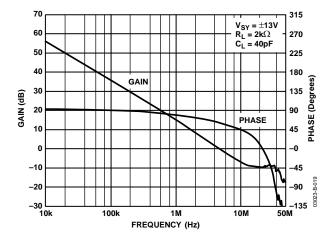

Figure 19. Open-Loop Gain and Phase Margin vs. Frequency

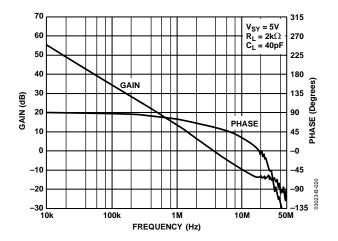

Figure 20. Open Loop Gain and Phase Margin vs. Frequency

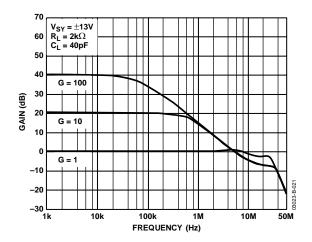

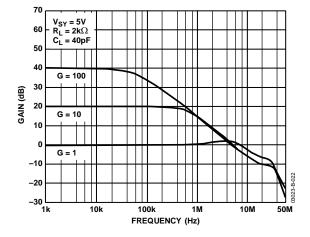

Figure 21. Closed-Loop Gain vs. Frequency

Figure 22. Closed-Loop Gain vs. Frequency

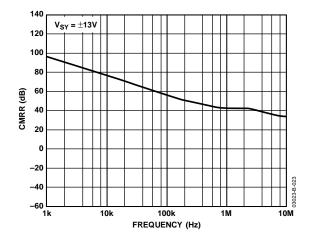

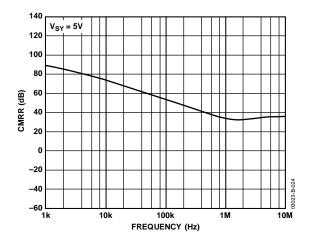

Figure 23. CMRR vs. Frequency

Figure 24. CMRR vs. Frequency

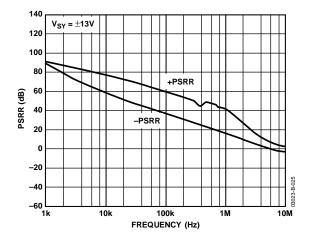

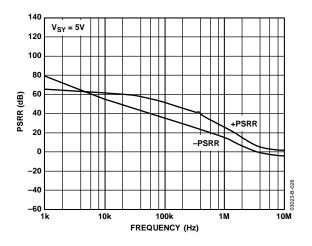

Figure 25. PSRR vs. Frequency

Figure 26. PSRR vs. Frequency

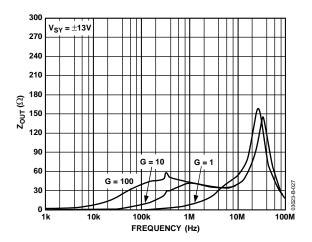

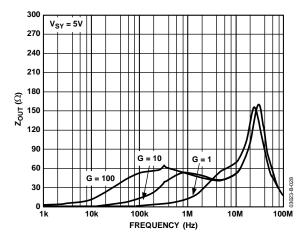

Figure 27. Output Impedance vs. Frequency

Figure 28. Output Impedance vs. Frequency

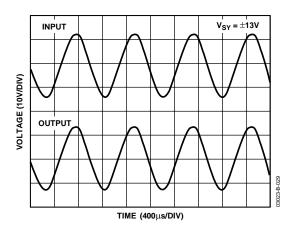

Figure 29. No Phase Reversal

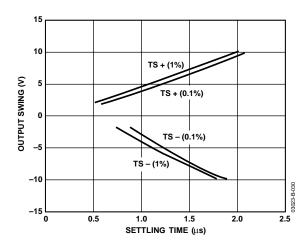

Figure 30. Output Swing and Error vs. Settling Time

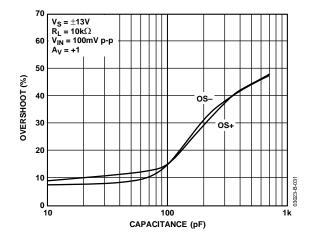

Figure 31. Small Signal Overshoot vs. Load Capacitance

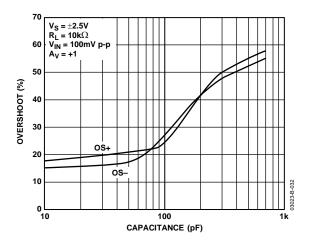

Figure 32. Small Signal Overshoot vs. Load Capacitance

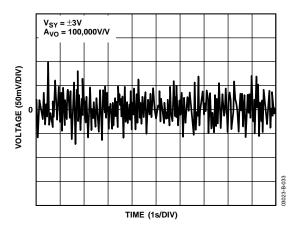

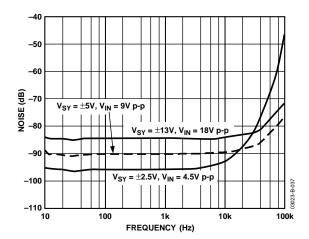

Figure 33. 0.1 Hz to 10 Hz Noise

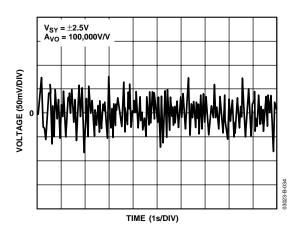

Figure 34. 0.1 Hz to 10 Hz Noise

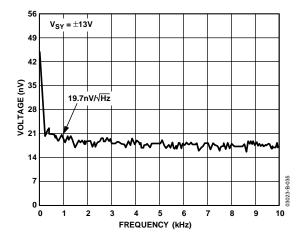

Figure 35. Voltage Noise Density

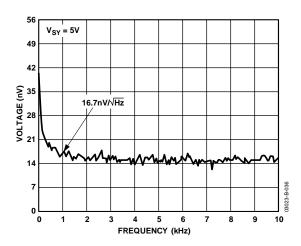

Figure 36. Voltage Noise Density

Figure 37. Total Harmonic Distortion + Noise vs. Frequency

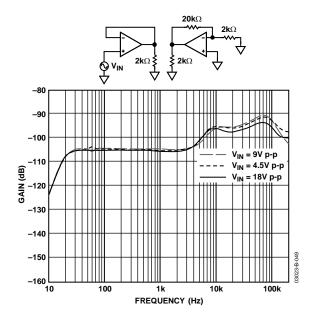

Figure 38. Channel Separation

#### **APPLICATIONS**

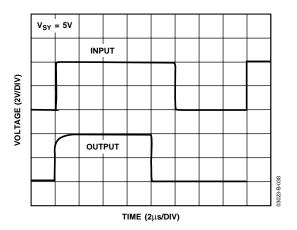

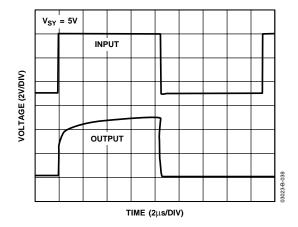

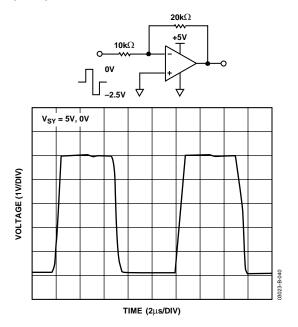

The AD862x is one of the smallest and most economical JFETs offered. It has true single-supply capability and has an input voltage range that extends below the negative rail, allowing the part to accommodate input signals below ground. The rail-to-rail output of the AD862x provides the maximum dynamic range in many applications. To provide a low offset, low noise, high impedance input stage, the AD862x uses n-channel JFETs The input common-mode voltage extends from 0.2 V below  $-V_{\rm S}$  to 2 V below  $+V_{\rm S}$ . Driving the input of the amplifier, configured in unity gain buffer, closer than 2 V to the positive rail causes an increase in common-mode voltage error, as illustrated in Figure 15, and a loss of amplifier bandwidth. This loss of bandwidth causes the rounding of the output waveforms shown in Figure 39 and Figure 40, which have inputs that are 1 V and 0 V from  $+V_{\rm S}$ , respectively.

The AD862x will not experience phase reversal with input signals close to the positive rail, as shown in Figure 29. For input voltages greater than  $+V_{SY}$ , a resistor in series with the AD862x's noninverting input prevents phase reversal at the expense of greater input voltage noise. This current limiting resistor should also be used if there is a possibility of the input voltage exceeding the positive supply by more than 300 mV, or if an input voltage is applied to the AD862x when  $\pm V_{SY} = 0$ . Either of these conditions will damage the amplifier if the condition exists for more than 10 seconds. A  $100 \text{ k}\Omega$  resistor allows the amplifier to withstand up to 10 V of continuous overvoltage, while increasing the input voltage noise by a negligible amount.

Figure 39. Unity Gain Follower Response to 0 V to 4 V Step

Figure 40. Unity Gain Follower Response to 0 V to 5 V Step

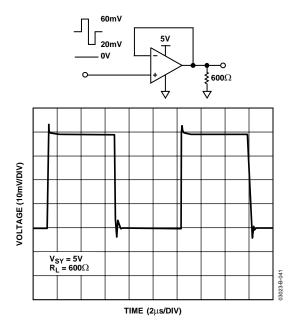

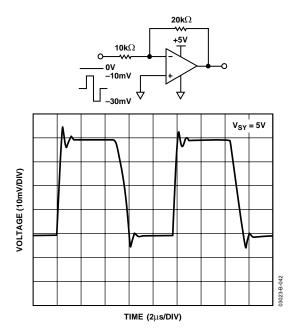

The AD862x can safely withstand input voltages 15 V below  $V_{SY}$  if the total voltage between the positive supply and the input terminal is less than 26 V. Figure 41 through Figure 43 show the AD862x in different configurations accommodating signals close to the negative rail. The amplifier input stage typically maintains picoamp-level input currents across that input voltage range.

Figure 41. Gain of Two Inverter Response to 2.5 V Step, Centered –1.25 V below Ground

Figure 42. Unity Gain Follower Response to 40 mV Step, Centered 40 mV above Ground

Figure 43. Gain of Two Inverter Response to 20 mV Step, Centered 20 mV below Ground

The AD862x is designed for  $16 \text{ nV/}\sqrt{\text{Hz}}$  wideband input voltage noise and maintains low noise performance to low frequencies, as shown in Figure 35. This noise performance, along with the AD862x's low input current and current noise, means that the AD862x contributes negligible noise for applications with large source resistances.

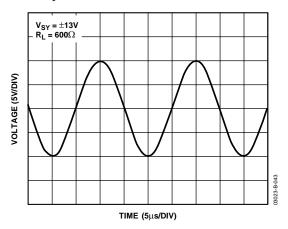

The AD862x has a unique bipolar rail-to-rail output stage that swings within 5 mV of the rail when up to 2 mA of current is drawn. At larger loads, the drop-out voltage increases as shown in Figure 17 and Figure 18. The AD862x's wide bandwidth and fast slew rate allows it to be used with faster signals than previous single-supply JFETs. Figure 44 shows the response of AD862x, configured in unity gain, to a  $V_{\rm IN}$  of 20 V p-p at 50 kHz. The FPBW of the part is close to 100 kHz.

Figure 44. Unity Gain Follower Response to 20 V, 50 kHz Input Signal

#### MINIMIZING INPUT CURRENT

The AD862x is guaranteed to 1 pA max input current with a  $\pm 13$  V supply voltage at room temperature. Careful attention to how the amplifier is used will maintain or possibly better this performance. The amplifier's operating temperature should be kept as low as possible. Like other JFET input amplifiers, the AD862x's input current doubles for every 10°C rise in junction temperature, as illustrated in Figure 8. On-chip power dissipation raises the device operating temperature, causing an increase in input current. Reducing supply voltage to cut power dissipation reduces the AD862x's input current. Heavy output loads can also increase chip temperature; maintaining a minimum load resistance of 1 k $\Omega$  is recommended.

The AD862x is designed for mounting on PC boards. Maintaining picoampere resolution in those environments requires a lot of care. Both the board and the amplifier's package have finite resistance. Voltage differences between the input pins and other pins as well as PC board metal traces may cause parasitic currents larger than the AD862x's input current, unless special precautions are taken. For proper board layout to ensure the best result, refer to the ADI website for proper layout seminar material. Two common methods of minimizing parasitic leakages that should be used are guarding of the input lines and maintaining adequate insulation resistance.

Contaminants such as solder flux on the board's surface and the amplifier's package can greatly reduce the insulation resistance between the input pin and traces with supply or signal voltages. Both the package and the board must be kept clean and dry.

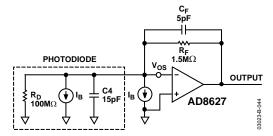

#### PHOTODIODE PREAMPLIFIER APPLICATION

The low input current and offset voltage levels of the AD862x, together with its low voltage noise, make this amplifier an excellent choice for preamplifiers used in sensitive photodiode applications. In a typical photovoltaic preamp circuit, shown in Figure 45, the output of the amplifier is equal to

$$V_{OUT} = -ID(Rf) = -R_p(P)Rf$$

where:

ID = photodiode signal current (A)

$R_p$  = photodiode sensitivity (A/W)

$R_f$  = value of the feedback resistor, in  $\Omega$

P =light power incident to photodiode surface, in W

The amplifier's input current,  $I_B$ , contributes an output voltage error proportional to the value of the feedback resistor. The offset voltage error,  $V_{OS}$ , causes a small current error due to the photodiode's finite shunt resistance,  $R_D$ .

The resulting output voltage error,  $V_E$ , is equal to

$$V_E = \left(1 + \frac{R_f}{R_D}\right) V_{OS} + Rf(I_B)$$

A shunt resistance on the order of 100 M $\Omega$  is typical for a small photodiode. Resistance  $R_D$  is a junction resistance that typically drops by a factor of two for every 10°C rise in temperature. In the AD862x, both the offset voltage and drift are low, which helps minimize these errors. With  $I_B$  values of 1 pA and  $V_{OS}$  of 50 mV,  $V_E$  for Figure 45 is very negligible. Also, the circuit in Figure 45 results in an SNR value of 95 dB for a signal bandwidth of 30 kHz.

Figure 45. A Photodiode Model Showing DC Error

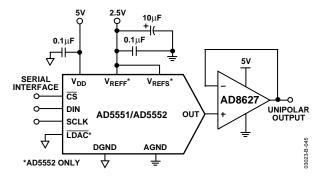

# OUTPUT AMPLIFIER FOR DIGITAL-TO-ANALOG CONVERTERS

Many system designers use amplifiers as buffers on the output of amplifiers to increase the DAC's output driving capability. The high resolution current output DACs need high precision amplifiers on their output as current to voltage converters (I/V). Additionally, many DACs operate with a single supply of 5 V. In a single-supply application, selection of a suitable op amp may be more difficult because the output swing of the amplifier does not usually include the negative rail, in this case AGND. This can result in some degradation of the DAC's specified performance unless the application does not use codes near zero. The selected op amp needs to have very low offset voltage—for a 14-bit DAC, the DAC LSB is 300 μV with a 5 V reference—to eliminate the need for output offset trims. Input bias current should also be very low because the bias current multiplied by the DAC output impedance (about 10 k $\Omega$  in some cases) adds to the zero code error. Rail-to-rail input and output performance is desired. For fast settling, the slew rate of the op amp should not impede the settling time of the DAC. Output impedance of the DAC is constant and code independent, but in order to minimize gain errors, the input impedance of the output amplifier should be as high as possible. The AD862x, with very high input impedance, I<sub>B</sub> of 1 pA, and fast slew rate, is an ideal amplifier for these types of applications. A typical configuration with a popular DAC is shown in Figure 46. In these situations, the amplifier adds another time constant to the system, increasing the settling time of the output. The AD862x, with 5 MHz of BW, helps in achieving a faster effective settling time of the combined DAC and amplifier.

Figure 46. Unipolar Output

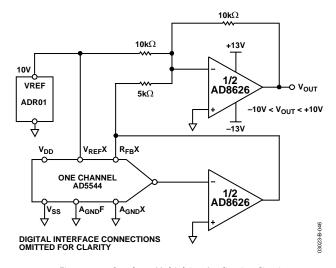

In applications with full 4-quadrant multiplying capability or a bipolar output swing, the circuit in Figure 47 can be used. In this circuit, the first and second amplifiers provide a total gain of 2, which increases the output voltage span to 20 V. Biasing the external amplifier with a 10 V offset from the reference voltage results in a full 4-quadrant multiplying circuit.

Figure 47. 4-Quadrant Multiplying Application Circuit

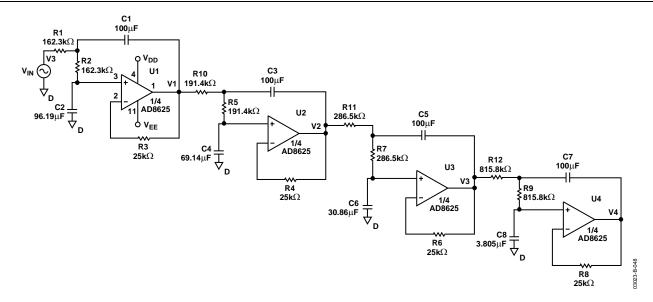

#### **EIGHT-POLE SALLEN KEY LOW-PASS FILTER**

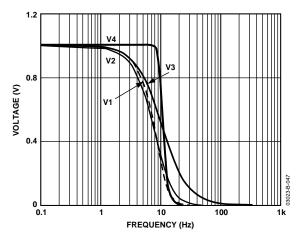

The AD862x's high input impedance and dc precision make it a great selection for active filters. Due to the very low bias current of the AD862x, high value resistors can be used to construct low frequency filters. The AD862x's picoamp-level input currents contribute minimal dc errors. Figure 49 shows an example, a 10 Hz, 8-pole Sallen Key filter constructed using the AD862x. Different numbers of the AD862x can be used depending on the desired response, which is shown in Figure 48. The high value used for R1 minimizes interaction with signal source resistance. Pole placement in this version of the filter minimizes the Q associated with the lower pole section of the filter. This eliminates any peaking of the noise contribution of resistors in the preceding sections, minimizing the inherent output voltage noise of the filter.

Figure 48. Frequency Response Output at Different Stages of the Low-Pass Filter

Figure 49. 10 Hz, 8-Pole Sallen Key Low-Pass Filter

#### **OUTLINE DIMENSIONS**

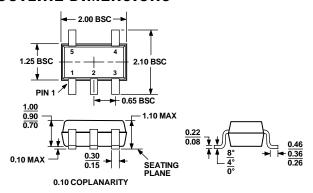

COMPLIANT TO JEDEC STANDARDS MO-203AA

Figure 50. 5-Lead Plastic Surface-Mount Package [SC70] (KS-5)Dimensions shown in millimeters

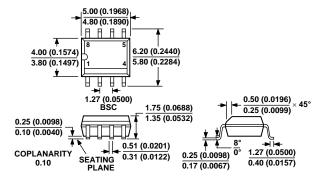

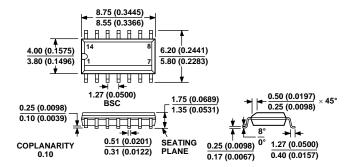

**COMPLIANT TO JEDEC STANDARDS MS-012AA** CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

Figure 51. 8-Lead Standard Small Outline Package [SOIC] Narrow Body (R-8)

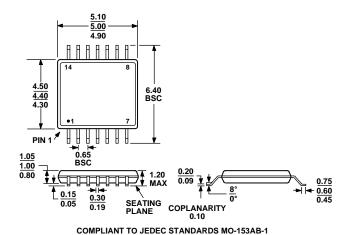

Figure 52. 8-Lead Mini Small Outline Package [MSOP] (RM-8) Dimensions shown in millimeters

COMPLIANT TO JEDEC STANDARDS MS-012AB CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS (IN PARENTHESES) ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

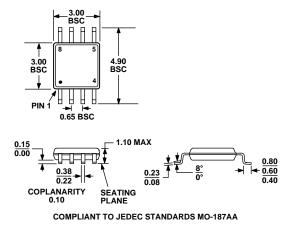

Figure 53. 14-Lead Standard Small Outline Package [SOIC] Narrow Body (R-14) Dimensions shown in millimeters and (inches)

Figure 54. 14-Lead Thin Shrink Small Outline Package [TSSOP]

(RU-14) Dimensions shown in millimeters

#### **ORDERING GUIDE**

| Model           | Temperature Range | Package Description | Package Option | Branding |

|-----------------|-------------------|---------------------|----------------|----------|

| AD8627AKS-REEL  | -40°C to +85°C    | 5-Lead SC70         | KS-5           | B9A      |

| AD8627AKS-REEL7 | -40°C to +85°C    | 5-Lead SC70         | KS-5           | B9A      |

| AD8627AKS-R2    | -40°C to +85°C    | 5-Lead SC70         | KS-5           | B9A      |

| AD8627AR        | -40°C to +85°C    | 8-Lead SOIC         | R-8            |          |

| AD8627AR-REEL   | -40°C to +85°C    | 8-Lead SOIC         | R-8            |          |

| AD8627AR-REEL7  | -40°C to +85°C    | 8-Lead SOIC         | R-8            |          |

| AD8626ARM-REEL  | -40°C to +85°C    | 8-Lead MSOP         | RM-8           | BJA      |

| AD8626ARM-R2    | -40°C to +85°C    | 8-Lead MSOP         | RM-8           | BJA      |

| AD8626AR        | -40°C to +85°C    | 8-Lead SOIC         | R-8            |          |

| AD8626AR-REEL   | -40°C to +85°C    | 8-Lead SOIC         | R-8            |          |

| AD8626AR-REEL7  | -40°C to +85°C    | 8-Lead SOIC         | R-8            |          |

| AD8625ARU       | -40°C to +85°C    | 14-Lead TSSOP       | RU-14          |          |

| AD8625ARU-REEL  | -40°C to +85°C    | 14-Lead TSSOP       | RU-14          |          |

| AD8625AR        | -40°C to +85°C    | 14-Lead SOIC        | R-14           |          |

| AD8625AR-REEL   | -40°C to +85°C    | 14-Lead SOIC        | R-14           |          |

| AD8625AR-REEL7  | -40°C to +85°C    | 14-Lead SOIC        | R-14           |          |

| AD8627/AD8626/AD8625 | Al | D8 | 36 | 27 | // | AE | 8( | 62 | 26/ | /A | D | 8 | 6 | 25 |  |

|----------------------|----|----|----|----|----|----|----|----|-----|----|---|---|---|----|--|

|----------------------|----|----|----|----|----|----|----|----|-----|----|---|---|---|----|--|

NOTES